Visible to Intel only — GUID: epi1481303814489

Ixiasoft

Visible to Intel only — GUID: epi1481303814489

Ixiasoft

3.4.1. Considerations for Connecting HPS to SDRAM

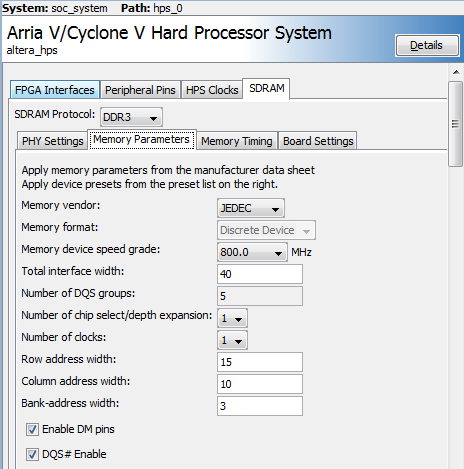

GUIDELINE: Ensure that the HPS memory controller Data Mask (DM) pins are enabled

In the HPS Component in Platform Designer (Standard), ensure that the checkbox to enable the data mask pins is enabled. If this control is not enabled, data corruption occurs any time a master accesses data in SDRAM that is smaller than the native word size of the memory.

Determine your SDRAM Memory type and bit width. Cyclone® V and Arria® V SoC devices offer DDR3, DDR2 and LPDDR2 SDRAM support for the HPS.

GUIDELINE: Ensure that you choose only DDR3, DDR2, or LPDDR2 components or modules in configurations supported by the Cyclone® V or Arria® V HPS EMIF for your specific device/package combination.

The External Memory Interface Spec Estimator, available on the External Memory Interface page, is a parametric tool that allows you to compare supported external memory interface types, configurations and maximum performance characteristics in Intel® FPGA and SoC devices.

First, filter the “Family” to select only Cyclone® V / Arria® V SoC device. Then, follow on by using the filter on “Interface Type” to choose only “HPS Hard Controller”

GUIDELINE: Ensure that in the HPS Component, the Memory Clock Frequency is supported by the device speed grade.

To obtain the maximum supported memory clock frequency for the device speed grade, refer to the External Memory Interface Spec Estimator, available on the External Memory Interface page.