Visible to Intel only — GUID: nfx1481305303679

Ixiasoft

1. Overview of the Design Guidelines for Cyclone® V SoC FPGAs and Arria® V SoC FPGAs

2. Background: Comparison between Cyclone® V SoC FPGA and Arria® V SoC FPGA HPS Subsystems

3. Design Guidelines for HPS portion of SoC FPGAs

4. Board Design Guidelines for SoC FPGAs

5. Embedded Software Design Guidelines for SoC FPGAs

A. Support and Documentation

B. Additional Information

4.2.1.1. Boot Source

4.2.1.2. Select Desired Flash Device

4.2.1.3. BSEL Options

4.2.1.4. Boot Clock

4.2.1.5. CSEL Options

4.2.1.6. Selecting NAND Flash Devices

4.2.1.7. Determine Flash Programming Method

4.2.1.8. For QSPI and SD/MMC/eMMC Provide Flash Memory Reset

4.2.1.9. Selecting QSPI Flash Devices

4.5.1. HPS EMAC PHY Interfaces

4.5.2. USB Interface Design Guidelines

4.5.3. QSPI Flash Interface Design Guidelines

4.5.4. SD/MMC and eMMC Card Interface Design Guidelines

4.5.5. NAND Flash Interface Design Guidelines

4.5.6. UART Interface Design Guidelines

4.5.7. I2C Interface Design Guidelines

4.5.8. SPI Interface Design Guidelines

5.1.1. Assembling the Components of Your Software Development Platform

5.1.2. Selecting an Operating System for Your Application

5.1.3. Assembling your Software Development Platform for Linux

5.1.4. Assembling a Software Development Platform for a Bare-Metal Application

5.1.5. Assembling your Software Development Platform for a Partner OS or RTOS

5.1.6. Choosing Boot Loader Software

5.1.7. Selecting Software Tools for Development, Debug and Trace

5.1.3.1. Golden System Reference Design (GSRD) for Linux

GUIDELINE: To successfully build your software development platform, it is recommended that you use the GSRD as a baseline project, then modify it to suit your application needs.

GUIDELINE: It is recommended that all new projects use the latest version of GSRD as a baseline.

5.1.3.2. Source Code Management Considerations

5.1.3.3. GSRD for Linux Development Flow

5.1.3.4. GSRD for Linux Build Flow

5.1.3.5. Linux Device Tree Design Considerations

5.5.1.1. Enable Runtime Calibration Report

5.5.1.2. Change DLEVEL To Get More Debug Information

5.5.1.3. Enable Example Driver for HPS SDRAM

5.5.1.4. Change Data Pattern in Example Driver

5.5.1.5. Example Code to Write and Read from All Addresses

5.5.1.6. Read/Write to HPS Register in Preloader

5.5.1.7. Check HPS PLL Lock Status in Preloader

Visible to Intel only — GUID: nfx1481305303679

Ixiasoft

5.1.3.1. Golden System Reference Design (GSRD) for Linux

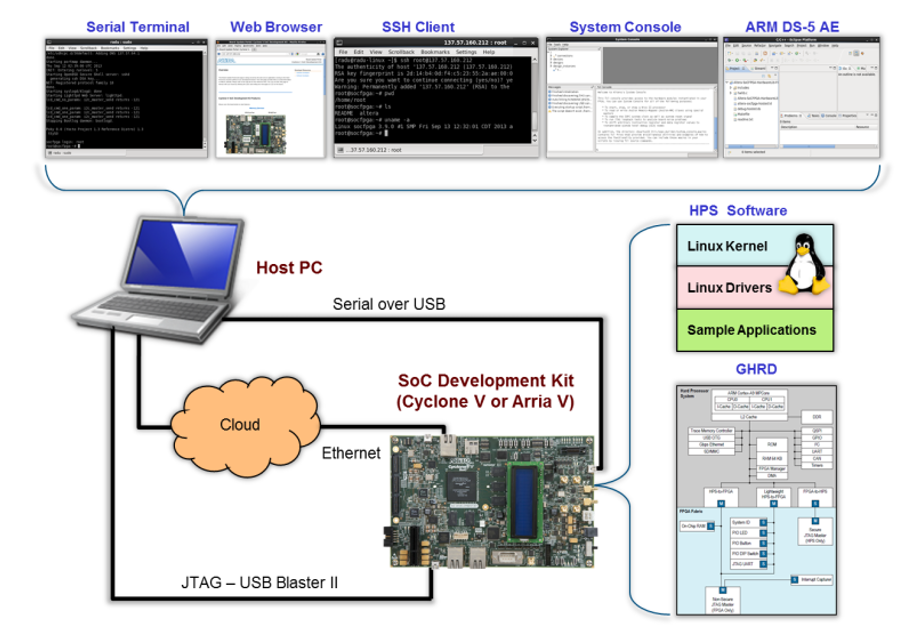

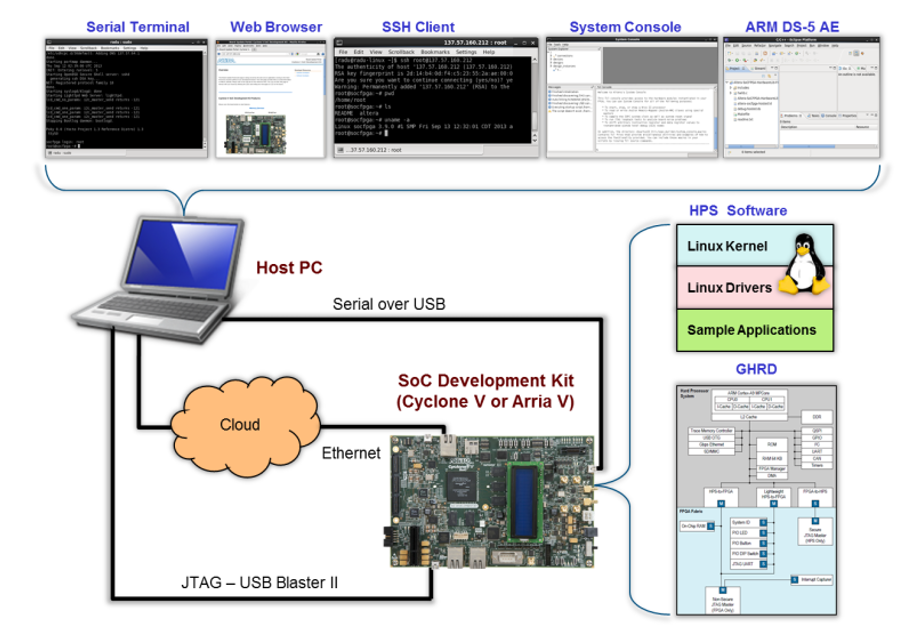

The Golden System Reference Design (GSRD) for Linux is provided, which consists of the following:

- GHRD (Golden Hardware Reference Design) - A Quartus Prime project

- Reference U-Boot based Bootloader

- Reference Linux BSP

- Sample Linux Applications

Figure 9. GSRD for Linux - Overview

The GSRD for Linux is a well-tested known good design showcasing a system using both HPS and FPGA resources, intended to be used as a baseline project.

GUIDELINE: To successfully build your software development platform, it is recommended that you use the GSRD as a baseline project, then modify it to suit your application needs.

The GSRDs target the Intel® SoC Development Boards and are provided both in source and pre-compiled form. They can be obtained from GSRD User Manuals.