Visible to Intel only — GUID: ufg1565894294760

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure (Beta)

2.4. Design Synthesis

2.5. Design Place and Route

2.6. Incremental Optimization Flow

2.7. Fast Forward Compilation Flow

2.8. Full Compilation Flow

2.9. Exporting Compilation Results

2.10. Integrating Other EDA Tools

2.11. Synthesis Language Support

2.12. Compiler Optimization Techniques

2.13. Synthesis Settings Reference

2.14. Fitter Settings Reference

2.15. Design Compilation Revision History

2.9.1. Exporting a Version-Compatible Compilation Database

2.9.2. Importing a Version-Compatible Compilation Database

2.9.3. Creating a Design Partition

2.9.4. Exporting a Design Partition

2.9.5. Reusing a Design Partition

2.9.6. Viewing Quartus Database File Information

2.9.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: ufg1565894294760

Ixiasoft

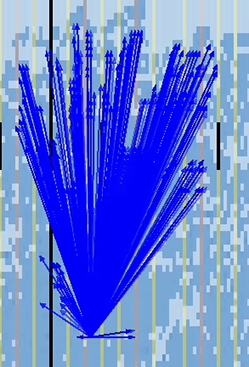

2.6.2.1.3. Analyzing High Fan-out Nets with Snapshot Viewer

- To run the Place or Route stage of the Fitter, double-click the stage in the Compilation Dashboard.

- After the stage completes, click the Snapshot Viewer icon for that stage in the Compilation Dashboard. The Snapshot Viewer opens.

- Under Analyze High Fanout Nets, click Show High Fanout Nets in the Schematic. The path displays and highlights in Tech Map Viewer for further analysis.

- Under Analyze High Fanout Nets, click Show High Fanout Nets in the Chip View. The path displays and highlights in the Chip Planner for further analysis.

Figure 71. Non-Global High Fan-Out Signal in Chip Planner