Visible to Intel only — GUID: kux1613963837075

Ixiasoft

Visible to Intel only — GUID: kux1613963837075

Ixiasoft

3.1.2. Refclk

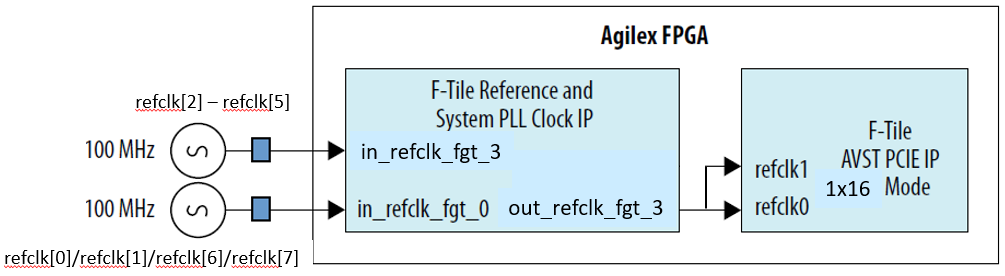

There are ten reference clock pins for FGT PMAs at the package level. Eight of the FGT reference clocks (refclk[0]-refclk[7]) can be used as reference clock inputs for PCI Express channels. There are up to four reference clock ports (refclk0 – refclk3) in the F-Tile Avalon Streaming IP for PCI Express depending on the Hard IP mode configuration in the IP. For Hard IP modes that span more than one FGT quads, you must use reference clock pins that are accessible by the quads. Depending on the HIP mode, you must assign the reference clock ports of the IP to corresponding reference clock pins in your Intel® Quartus® Prime design.

The F-Tile Reference and System PLL Clocks Intel FPGA IP is a required IP for F-tile Avalon Streaming PCI Express designs. It configures the reference clock for the PCI Express channels and also configures the System PLL.

The table below shows the mapping of reference clock pins to the reference clock ports of the F-Tile Avalon Streaming IP for PCI Express depending on the Hard IP mode.

| Mode | refclk0 port | refclk1 port | refclk2 port | refclk3 port |

|---|---|---|---|---|

| 1 x16 | refclk[2] or refclk[3] or refclk[4] or refclk[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] pin | N/A | N/A |

| 1 x8 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 2 x8 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin | N/A | N/A |

| 1 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 2 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | N/A | N/A |

| 4 x4 | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin | refclk[0] or refclk[1] or refclk[2] or refclk[3] or refclk[4] or reflck[5] pin | refclk[2] or refclk[3] or refclk[4] or refclk[5] or refclk[6] or reflck[7] pin |

- For 1 x16, 1 x8 and 1 x4 modes, both refclk0 and refclk1 ports need to be connected to a single outrefclk_fgt_i (i = 0 to 7) port from “F-Tile Reference and SystemPLL Clocks” IP.

- For 2 x8, 2 x4 and 4 x4 modes, user has an option to share a single refclk source across all the refclk port, connect to a single outrefclk_fgt_i (i = 0 to 7) port from “F-Tile Reference and SystemPLL Clocks” IP.

- Independent refclk source is supported for 2 x4, 2 x8 and 4 x4 modes.

In 2x8 mode, you can drive the refclk0 and refclk1 ports with either a single 100 MHz clock source connected to a reference clock pin at package level, or two independent 100 MHz sources depending on your system architecture. For example, if your system has each x8 port connected to a separate CPU/Root Complex, it may be necessary to drive the reference clock pins using independent clock sources. PERST# needs to indicate the stability of the clock source.

In 4x4 mode, you can drive the refclk0 to refclk3 ports with either a single 100 MHz clock source connect to a reference clock pin at package level, or two independent 100 MHz clock sources or four independent clock sources depending on your system architecture. PERST# needs to indicate the stability of the clock source.

- If compliance to PCIe link training timing specifications is required, the reference clock to the System PLL must be available and stable before device configuration begins. You must set the Refclk is available at power-on parameter in the System PLL IP to On. Derive the reference clock from an independent and free-running clock source. Alternatively, if the reference clock from the PCIe link is guaranteed available before device configuration starts, you can use it to drive the System PLL. Once the PCIe link refclk is alive, it can never be allowed to go down.

- If compliance to PCIe link training timing specifications is not required and the reference clock to the System PLL may not be available before device configuration starts, you must set the Refclk is available at power-on parameter in the System PLL IP to Off. In this case, you may use the reference clock from the PCIe link to drive the System PLL. The System PLL does not lock to the reference clock until you perform the global Avalon memory-mapped interface write operations signaling that the reference clock is available.

The figure below shows an example where an independent reference clock drives the System PLL (via the in_refclk_fgt_0 port). It does not share the reference clock from the PCIe link which is not available before device configuration starts.

Once the reference clock for the System PLL is up, it must be stable and present throughout the device operation and must not go down. If you are not able to adhere to this requirement, you must reconfigure the device.