Visible to Intel only — GUID: wvf1617310042704

Ixiasoft

Visible to Intel only — GUID: wvf1617310042704

Ixiasoft

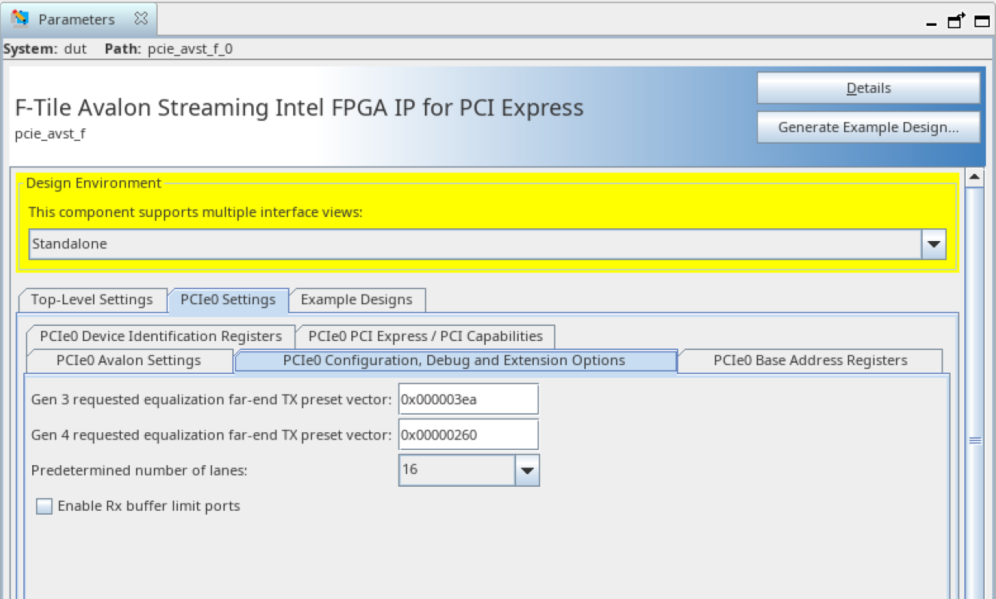

6.2.5. Configuration, Debug and Extension Options

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Gen 3 Requested equalization far-end TX preset vector | 0 - 65535 | 0x00000020 (for F-Tile devices with OPNs that end with the suffix VR0, VR1, or VR2) 0x0000030a (for F-Tile devices with OPNs that end with the suffix VR3 or AA) |

Specifies the Gen 3 requested phase 2/3 far-end TX preset vector. |

| Gen 4 Requested equalization far-end TX preset vector | 0 - 65535 | 0x00000020 (for F-Tile devices with OPNs that end with the suffix VR0, VR1, or VR2) 0x00000060 (for F-Tile devices with OPNs that end with the suffix VR3 or AA) |

Specifies the Gen 4 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs.

Note: In Intel® Quartus® Prime Pro Edition version 23.1, the default value of this parameter is incorrectly set to 0x00000060 for F-Tile devices with OPNs that end with the suffix VR3 or AA. You are required to set this value to 0x00000260 manually before IP generation.

|

| Enable RX Buffer Limit Ports | True/False | False | When selected, RX buffer limit ports are exported allowing you to control the buffer limits for RX Posted, Non-Posted and CplD packets. Otherwise, the Maximum Buffer Size is used. |

| Predetermined number of lanes | 16 8 4 2 1 |

Maximum link width | Defines the number of lanes which are connected and good. Used to limit the effective link width to ignore 'broken" or "unused" lanes that detect a receiver. Indicates the number of lanes to check for exit from Electrical Idle in Polling.Active and L2.Idle. It is possible that the LTSSM might detect a receiver on a bad or broken lane during the Detect Substate. However, it is also possible that such a lane might also fail to exit Electrical Idle and therefore prevent a valid link from being configured. This value is referred to as the "Predetermined Number of Lanes" in section 4.2.6.2.1 of the PCI Express Base Specification. When you have unused lanes in the system, you must change the value in this register to reflect the number of lanes. For instance, if you find that one of the used lanes is bad, then you must reduce the value of "Predetermined number of lanes". |

| Enable Prefetchable Memory 64-bit address support |

True/False |

True |

When in RP mode, indicates that the prefetchable memory range supported is 64-bit. |