Visible to Intel only — GUID: iga1458085899668

Ixiasoft

Visible to Intel only — GUID: iga1458085899668

Ixiasoft

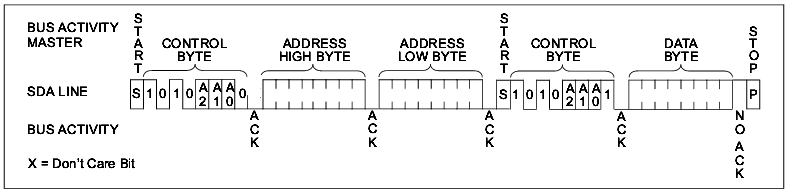

16.2.4.1. Random Address Read

Random read operations allow the upstream I2C host to access any memory location in a random manner. To perform this type of read operation, you must first set the byte address. The I2C host issues a byte address to the bridge as part of a write operation then followed by a read command. After the read command is issued, the internal address counter points to the address location following the one that was just read. The upper address bits are transferred first, followed by the LSB(s).