Visible to Intel only — GUID: iga1458085933495

Ixiasoft

Visible to Intel only — GUID: iga1458085933495

Ixiasoft

16.2.5. Write Operation

The Avalon® write data width is 32 bits wide. A 32-bit width limits the bridge to only issue word align Avalon® addresses. It also allows the upstream I2C host to write to any sequence of bytes on any address alignment. There is a conversion logic which sits between the Avalon® interface and the I2C interface.

Write operation conversion logic flow:

- Checks the address alignment issued by the I2C host.

- Enables data by setting byteenable high to indicate which byte address the I2C host wants to write into.

Note: If the address issued by I2C host is 0x03h, the byteenable is 4’b1000.

- Combines multiple bytes of data into a 32-bit packet if their addresses are sequential.

Note: If the first write is to address 0x04 and the second write is to address 0x05, then byteenable is 4’b0011.

Legal byteenable combinations are 4’b0001, 4’b0010, 4’b0100, 4’b1000, 4’b0011, 4’b1100 and 4’b1111.

- If the write request issued by the I2C host ends up with an illegal byteenable combination such as, 4’b0110, 4’b0111, or 4’b1110, then the bridge generates multiple Avalon® byte writes.

Note: If the sequential write request from the I2C host starts from 0x0 and ends at 0x02 (illegal byteenable, b’0111), then the bridge will generate three Avalon® write requests with legal byteenable 4’b0001, 4’b0010 and 4’b0100.

- Issues a word align Avalon® address according to the address sent by the I2C host with the two LSB set to zero.

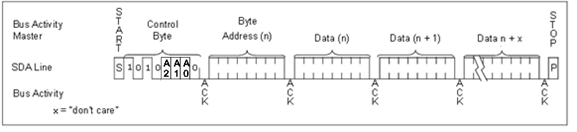

Upon receiving of the agent address with the R/W bit set to zero, the bridge issues an acknowledge to the I2C host. The next byte transmitted by the host is the byte address. The byte address is written into the address counter inside the bridge. The bridge acknowledges the I2C host again and the host transmits the data byte to be written into the addressed memory location. The host keeps sending data bytes to the bridge and terminates the operation with a Stop condition at the end.