2.3.1. Testbench

The testbench uses a test driver module, altpcietb_bfm_rp_gen4_x16.sv, to initiate the configuration and memory transactions. At startup, the test driver module displays information from the Root Port and Endpoint Configuration Space registers, so that you can correlate to the parameters you specified using the Parameter Editor.

The example design and testbench are dynamically generated based on the configuration that you choose for the P-Tile IP for PCIe. The testbench uses the parameters that you specify in the Parameter Editor in Intel® Quartus® Prime.

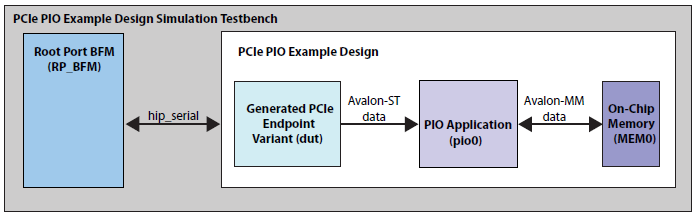

This testbench simulates up to a ×16 PCI Express link using the serial PCI Express interface. The testbench design does allow more than one PCI Express link to be simulated at a time. The following figure presents a high level view of the PIO design example.

- altpcietb_bfm_rp_gen4x16.sv —This is the Root Port PCIe* BFM.

//Directory path <project_dir>/intel_pcie_ptile_ast_0_example_design/pcie_ed_tb/ip/pcie_ed_tb/dut_pcie_tb_ip/intel_pcie_ptile_tbed_<ver>/sim - pcie_ed_dut.ip: This is the Endpoint design with the parameters that you specify.

//Directory path <project_dir>/intel_pcie_ptile_ast_0_example_design/ip/pcie_ed - pcie_ed_pio0.ip: This module is a target and initiator of transactions for the PIO design example.

//Directory path <project_dir>/intel_pcie_ptile_ast_0_example_design/ip/pcie_ed - pcie_ed_sriov0.ip: This module is a target and initiator of transactions for the SR-IOV design example.

//Directory path <project_dir>/intel_pcie_ptile_ast_0_example_design/ip/pcie_edFigure 16. SR-IOV Design Example Simulation Testbench

In addition, the testbench has routines that perform the following tasks:

- Generates the reference clock for the Endpoint at the required frequency.

- Provides a PCI Express reset at start up.

For more details on the Root Port BFM, refer to the TestBench chapter of the Intel FPGA P-Tile Avalon® streaming IP for PCI Express User Guide.