Visible to Intel only — GUID: bkk1591633569414

Ixiasoft

2.6.1. Running the PIO Design Example

- Navigate to ./software/user/example under the design example directory.

- Compile the design example application:

$ make

- Run the test:

$ sudo ./intel_fpga_pcie_link_test

You can run the Intel® FPGA IP PCIe* link test in manual or automatic mode. Choose from:- In automatic mode, the application automatically selects the device. The test selects the Intel PCIe* device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function number and BAR.

For the Intel® Stratix® 10 DX or Intel® Agilex™ Development Kit, you can determine the BDF by typing the following command:

$ lspci -d 1172:

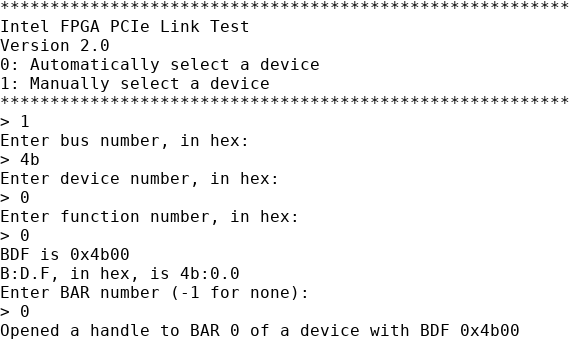

- Here are sample transcripts for automatic and manual modes:

Automatic mode:

Intel FPGA PCIe Link Test - Automatic Mode Version 2.0 0: Automatically select a device 1: Manually select a device *************************************************** >0 Opened a handle to BAR 0 of a device with BDF 0x100 *************************************************** 0: Link test - 100 writes and reads 1: Write memory space 2: Read memory space 3: Write configuration space 4: Read configuration space 5: Change BAR 6: Change device 7: Enable SR-IOV 8: Do a link test for every enabled virtual function belonging to the current device 9: Perform DMA 10: Quit program *************************************************** > 0 Doing 100 writes and 100 reads . . Number of write errors: 0 Number of read errors: 0 Number of DWORD mismatches: 0

Manual mode:

Related Information