1.2. Generating the Design

Configure the SDI II Intel® FPGA IP parameter editor in the Quartus® Prime software to generate the design examples.

Figure 3. Generating the Design Flow

- Create an empty project targeting Agilex™ 5 device family and select the desired device.

- In the IP Catalog, locate and double-click GTS SDI II Intel® FPGA IP . The IP Parameter Editor window appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip>.ip or <your_ip>.qsys.

- Click OK. The parameter editor appears.

- On the IP main tab, select your desired IP settings. The generated design example is based on your settings.

- In the SDI_II wrapper 3 option, select Both Base and PHY option for integrated PHY design or BASE only option for separate PHY design.

- On the IP Analog Parameters tab, select your desired analog parameter settings. The generated design example is based on your settings.

Note: The RX Adaptation mode option in the IP Analog Parameters tab is fixed to manual as SDI does not support auto adaptation.

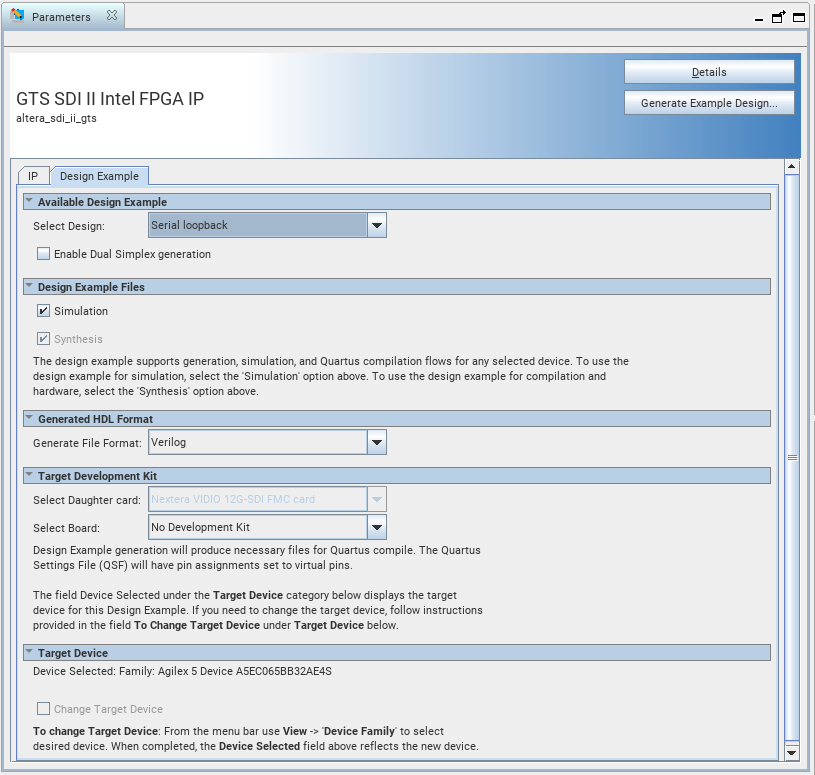

- On the Design Example tab, select the desired parameter for the design example. Select Simulation to generate the testbench.

- To generate the design example with DS groups: In the IP main tab, select Both Base and PHY option. In the Design Example tab, select the Enable Dual Simplex Generation option.

- Select Simulation to generate the testbench and select Synthesis to generate the hardware design example.

- For Target Development Kit, select the relevant FPGA development kit. You may change the target device using the Change Target Device parameter if your board revision does not match the grade of the default targeted device.

- Click Generate Example Design button to initiate the design generation.

Figure 4. Design Example Tab in SDI II IP Parameter Editor

3 SDI_II wrapper option allows you to generate design with SDI II IP cores with the PHY directly integrated when you choose Both BASE and PHY. If you choose BASE only, you can change the transceiver setting in PHY IP based on your needs.