Visible to Intel only — GUID: xid1637117291484

Ixiasoft

1. GTS SDI II Intel® FPGA IP Design Example Quick Start Guide

2. Design Example Detailed Description

3. GTS SDI II Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs Archives

4. Document Revision History for the GTS SDI II Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

Visible to Intel only — GUID: xid1637117291484

Ixiasoft

1.3. Compiling and Simulating the Design

The GTS SDI II Intel® FPGA IP design example testbench simulates one channel serial loopback design with TX instance connected to an internal video pattern generator. The serial output from the TX instance connects to the RX instance in the testbench. The testbench also includes checkers and control mechanisms.

Figure 5. Simulating the Design Flow

To run example design simulation, follow these steps:

- Generate the necessary simulation setup files.

- Go to simulation folder.

- Go to the desired simulator folder and run the simulation script:

- ModelSim* SE or QuestaSim* FE: Bring up the simulator GUI, change directory to mentor folder and type do mentor.do

- VCS* MX : Go to synopsys/vcsmx folder and type source vcsmx_sim.sh

- Xcelium* : Go to xcelium folder and type source xcelium_sim.sh

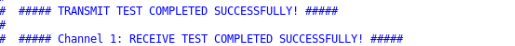

- A successful simulation ends with the following message: