Visible to Intel only — GUID: jyf1705618360569

Ixiasoft

Visible to Intel only — GUID: jyf1705618360569

Ixiasoft

3.5.1.1. Confirming Agilex™ 7 FPGA I-Series Transceiver-SoC Development Kit Board Set Up

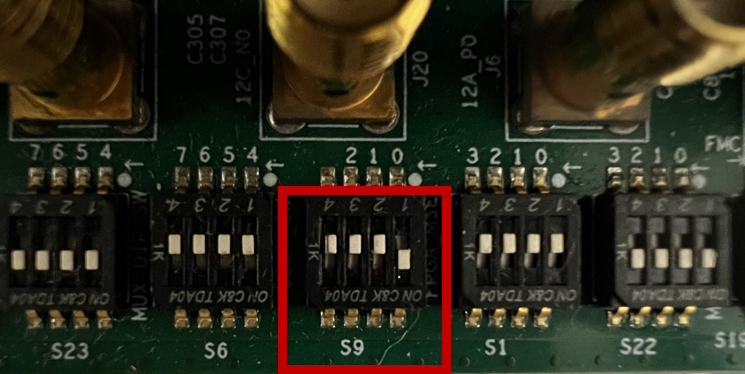

- Ensure that the Agilex™ 7 FPGA I-Series Transceiver-SoC Development Kit has the required DIP switch and jumper settings. The SoC example design requires that all DIP switches have their default settings except for S9 where switch 1 is ON and switches 2,3, and 4 are OFF:

For more details about default DIP switch and jumper settings, refer to Agilex™ 7 FPGA I-Series Transceiver-SoC Development Kit User Guide .

- Ensure that the HPS IO48 OOBE daughter card is installed in connector J4 on the development kit, and the SD card with the programmed Yocto image is installed in the daughter card.

- Ensure that the DDR4 x8 RDIMM is installed in the PCIe slot furthest from the fan. For RDIMM requirements, refer to Agilex 7 FPGA I-Series Transceiver-SoC Development Kit Hardware Requirements.

When configured and connected, the Agilex™ 7 FPGA I-Series Transceiver-SoC Development Kit should resemble the following image:

-

The USB 2.0 connector is used to program the FPGA device.

-

The Ethernet connector is used for fast data transfer to the HPS.

-

The micro USB connector is used to monitor the serial output from, and provide command-line input to the HPS during operation.