Visible to Intel only — GUID: oua1665161403922

Ixiasoft

Visible to Intel only — GUID: oua1665161403922

Ixiasoft

7.1. Using the Intel FPGA PTC to Estimate NoC Power

To estimate NoC power using the Intel FPGA PTC, follow these steps:

- To open the Intel FPGA PTC from the Intel Quartus Prime Pro Edition software, click Tools > Power and Thermal Calculator

- Open the Main page and ensure that the selected device, device grade and transceiver grade match your device. NoC power estimation is only available for Intel® Agilex® 7 M-Series FPGAs.

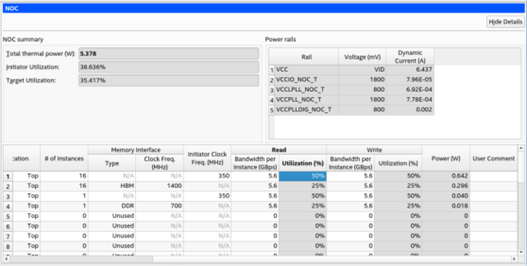

Figure 32. Example Intel FPGA PTC NOC Page

- Select the NOC page. Use any scrollbars along the right and bottom sides of the table to view additional rows or columns available for entry.

The top portion of the Intel FPGA PTC shows results that calculate from the table at the bottom portion of the Intel FPGA PTC. These results include the NOC summary of total power, and the initiator and target utilization. The total power includes the power usage of the initiators and targets in the table, as well as the power usage of the hard memory NoC itself, and its supporting NoC PLL and NoC SSM. A breakdown of current draw per power rail also appears.

- Enter information about initiators and targets in your design in the table in the bottom portion of the Intel FPGA PTC. You can edit the Entity Name and Full Hierarchy Name fields. The report includes these two optional columns if you use them, and displays them in the PTC Module Manager.

- In the Block Type column, select whether the element on that row is an Initiator or a Target.

- In the Location column, select whether that initiator or target is associated with the hard memory NoC along the top edge of the die, or the hard memory NoC along the bottom edge of the die.

- In the # of Instances column, enter the number of initiator or target interface bridges for the element on this row.

Note: A single NoC Initiator Intel FPGA IP can contain multiple initiator interface bridges. Similarly, a target memory IP, such as the High Bandwidth Memory (HBM2E) Interface Intel® Agilex® 7 FPGA IP, can contain multiple target interface bridges. This Intel FPGA PTC page only reflects the power usage of the NoC targets of IP, such as the High Bandwidth Memory (HMB2E) Interface Intel® Agilex® 7 FPGA IP. Estimate the power for the remainder of this IP elsewhere within the Intel FPGA PTC, for example on the HBM page.

- For target elements only, specify details about the Memory Interface. In the Type column, select either HBM for HBM2e memory or DDR for external memory interfaces implemented in GPIO-B blocks. In the Clock Freq. (MHz) column, enter the clock frequency for these target interface bridges.

- For initiator elements only, use Initiator Clock Freq. (MHz) column to enter the clock frequency that the user interface for these initiators operates. If different initiators operate at different frequencies, you must specify each frequency on a separate row.

- For both initiator and target elements, use the Read and Write Bandwidth per Instance (GBps) columns to specify read and write bandwidth. This entry is for the read or write bandwidth for each instance and expressed in MBps. The Utilization (%) displays the bandwidth utilization for each initiator or target. You must specify Initiator or target elements with different bandwidth requirements on separate rows.

The following fields display the PTC results:

- The Utilization (%) field displays the bandwidth utilization for each initiator or target.

- Power (W) displays the power for the total initiators or targets specified on that row.

- User Comment is a text field that you can edit that appears in the results report.

- NoC initiators that have AXI4 read data widths greater than or equal to 512 bits use the fabric NoC to return read data via M20K memory blocks. For each initiator that has an AXI4 read data width greater than or equal to 512 bits, create an entry on this table with the RAM Type set to M20K and # of Instances set to 16.

- Set the Vertical Network to Top or Bottom, based on the hard memory NoC that connects to the initiator. The Vertical Network Column specifies which column of M20K memory blocks the Fabric NoC is in. Make this column value unique for each initiator on the same edge of the device.

- Set the Data Width to 32 and the RAM Depth to 512. With the Vertical Network set to Top or Bottom, the RAM Mode automatically sets to Simple Dual Port. The parameters for Port A are based on the NoC operation that runs at 700 MHz in -1 and -2 speed grade devices, and at 500 MHz in -3 speed grade devices. The parameters for Port B are based on the AXI4 clock for the read interface of the initiator. The parameters for the Vertical Network Port set according to the expected traffic from the HBM2e or external memory.