Visible to Intel only — GUID: klc1638580197736

Ixiasoft

Visible to Intel only — GUID: klc1638580197736

Ixiasoft

4.5.2.1.3. Software Design Flow (Bootloader via SDM Project)

Creating the Bootloader via SDM BSP Project

To launch the BSP Editor, follow these steps:

- In the Platform Designer window, select File > New BSP. The Create New BSP windows appears.

- For BSP setting file, navigate to the software/mailbox_bootloader/bsp folder and name the BSP as settings.bsp.

BSP path: <project directory>/software/mailbox_bootloader/bsp/settings.bsp

- For System file (qsys or sopcinfo), select the Nios® V processor Platform Designer system (.qsys) file.

- For Quartus project, select the Quartus Project File.

- For Revision, select the correct revision.

- For CPU name, select the Nios® V processor.

- Select the Operating system as Altera HAL.

- Click Create to create the BSP file.

Configuring BSP Editor and Generating the BSP Project

- Go to BSP Editor > Main > Settings

- Configure the settings per the following table:

:

Table 31. Settings for BSP Editor Settings Action hal.max_file_descriptors 5

Input as 4 hal.log_port 5

Select as None hal.enable_exit 5

hal.enable_clean_exit 5

hal.c_plus_plus 5

Unchecked to disable the feature. hal.sys_clk_timer 5

hal.timerstamp_timer 5

hal.stdin 5

hal.stdout 5

hal.stderr 5

Select as None hal.linker Enable the following settings:

• allow_code_at_reset

• enable_alt_load

• enable_alt_load_copy_rodata

• enable_alt_load_copy_rwdata

• enable_alt_load_copy_exceptions

hal.make.cflags_user_flags 5

Input as -ffunction-sections -fdata-sections hal.make.link_flags 5

Input as -Wl,--gc-sections hal.make.cflags_optimization 5

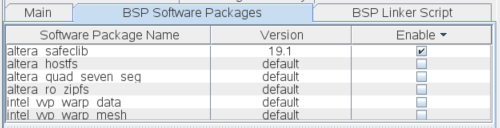

Input as -Os Figure 54. hal SettingsFigure 55. hal.linker SettingsFigure 56. hal.toolchain SettingsFigure 57. hal.make Settings - Go to BSP Software Package and enable altera_safeclib

Figure 58. BSP Software Package

- Click the BSP Linker Script tab in the BSP Editor.

- Set the .text item in the Linker Section Name to the Bootloader ROM in the Linker Region Name. Set the rest of the items in the Linker Section Name list to the Bootloader RAM.

Figure 59. Linker Region Settings

- Navigate to the BSP Driver tab and disable all drivers (except the Nios® V Processor and Mailbox Client Intel® FPGA IP).

Figure 60. BSP Driver tab

- Click Generate BSP. Make sure the BSP generation is successful.

- Close the BSP Editor.

Create the Bootloader via SDM Application Project

- Download the example design files (Refer to Bootloader via SDM Example Design section). You do not need to build the example design.

- Navigate to the sw/mailbox_bootloader/app folder in the Bootloader via SDM Example Design project.

- Copy the Bootloader via SDM (mailbox_bootloader.c) into the software/mailbox_bootloader/app folder in your project.

- Redefine the PAYLOAD_OFFSET in mailbox_bootloader.c.

Note: The SOF image size influences the PAYLOAD_OFFSET. The PAYLOAD_OFFSET is the start address of the Nios® V application HEX file in QSPI flash and must point to a location after the SOF image. You can determine the minimum PAYLOAD_OFFSET by using the configuration bitstream size from the device datasheet.

For example, the estimated compressed configuration bitstream size for Intel Stratix 10 SX 2800 is 577 Mbits (72.125 MBytes). The actual size can be equal or smaller than this bitstream size. If the SOF image starts at address 0x0, the SOF image should reached until address 0x44C8FFF (0x44C8A48). With that, the minimum PAYLOAD_OFFSET you can select is 0x4500000.

- Launch the Nios V Command Shell.

- Execute the command below to generate the Bootloader via SDM application CMakeLists.txt.

niosv-app --app-dir=software/mailbox_bootloader/app\ --bsp-dir=software/mailbox_bootloader/bsp\ --srcs=software/mailbox_bootloader/app/mailbox_bootloader.c

Building the Bootloader via SDM Project

You can choose to build the Bootloader via SDM project using the RiscFree* IDE for Intel FPGAs or through the command line interface (CLI).

With the CLI , you can build the Bootloader via SDM using the following commands:

cmake -G "Unix Makefiles" -DCMAKE_BUILD_TYPE=Release -B \

software/mailbox_bootloader/app/release -S \

software/mailbox_bootloader/app

make -C software/mailbox_bootloader/app/release

The Bootloader via SDM (.elf) file is created in

software/mailbox_bootloader/app/release folder.

Generating the HEX File and Initializing the Memory

A HEX file must be generated from the ELF file so that the HEX file can be used for memory initialization.

- Launch the Nios V Command Shell.

- For Bootloader via SDM, use the following command line to convert the ELF to HEX. This command creates the Bootloader via SDM (bootcopier_rom.hex) file.

elf2hex software/mailbox_bootloader/app/release/app.elf \ -o bootcopier_rom.hex \ -b <base address of Bootloader ROM> \ -w <data width of Bootloader ROM in bits> \ -e <end address of Bootloader ROM> \ -r <data width of Bootloader ROM in bytes>

Recompile the hardware design to memory-initialize the bootcopier_rom.hex into the Bootloader ROM.