1.3. Generating the Design Example

Figure 4. Procedure

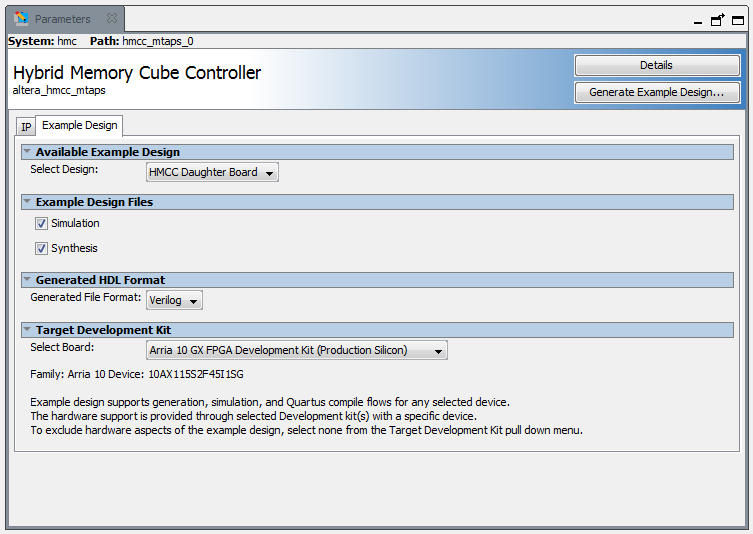

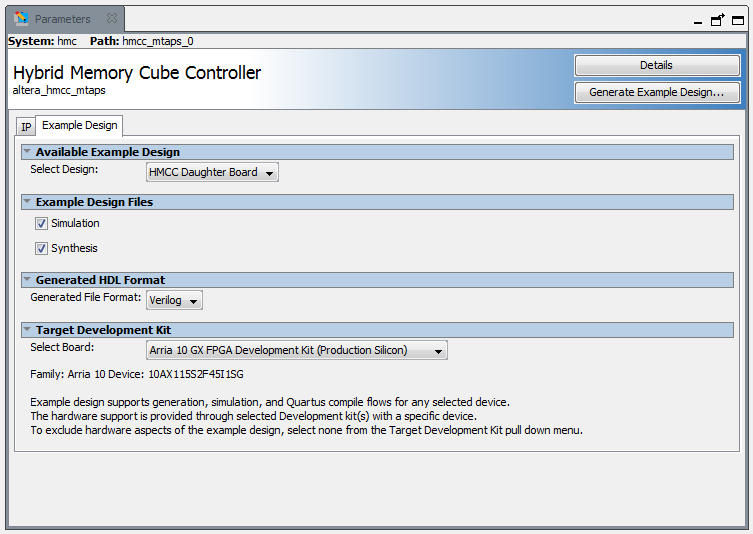

Figure 5. Example Design Tab in Hybrid Memory Cube Controller Parameter Editor

Follow these steps to generate the Arria 10 hardware design example and testbench:

- In the IP Catalog (Tools > IP Catalog), select the Arria 10 target device family.

- In the IP Catalog, locate and select Hybrid Memory Cube Controller. The New IP Variation window appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip> .qsys .

- You must select a specific Arria 10 device in the Device field, or keep the default device the Quartus Prime software selects.

- Click OK. The IP parameter editor appears.

- On the IP tab, specify the parameters for your IP core variation.

- On the Example Design tab, choose the following settings for the design example:

- For Select Design, select the HMCC Daughter Board option.

- For Example Design Files, select the Simulation option to generate the testbench, and select the Synthesis option to generate the hardware design example.

- For Generated HDL Format, only Verilog is available.

- For Target Development Kit select the Arria 10 GX FPGA Development Kit (Production Silicon).

Note:

When you choose this kit, the hardware design example overwrites your previous device selection with the device on the target board.

When you generate the design example, the Intel® Quartus® Prime software creates Intel® Quartus® Prime project, setting, and pin assignments for the board you selected. If you do not want the software to target a specific board, select None.

- Click the Generate Example Design button.