Visible to Intel only — GUID: olj1606728958898

Ixiasoft

1. About the PHY Lite for Parallel Interfaces IP

2. PHY Lite for Parallel Interfaces FPGA IP for Agilex™ 5 D-Series and E-Series Devices

3. PHY Lite for Parallel Interfaces FPGA IP for Agilex™ 7 M-Series Devices

4. PHY Lite for Parallel Interfaces FPGA IP for Agilex™ 7 F-Series and I-Series Devices

5. PHY Lite for Parallel Interfaces FPGA IP for Stratix® 10 Devices

6. PHY Lite for Parallel Interfaces FPGA IP for Arria® 10 and Cyclone® 10 GX Devices

7. PHY Lite for Parallel Interfaces FPGA IP User Guide Document Archives

8. Document Revision History for the PHY Lite for Parallel Interfaces FPGA IP User Guide

5.5.6.4.1. Timing Closure: Dynamic Reconfiguration

5.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

5.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

5.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

5.5.6.4.5. I/O Timing Violation

5.5.6.4.6. Internal FPGA Path Timing Violation

6.5.6.4.1. Timing Closure: Dynamic Reconfiguration

6.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

6.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

6.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

6.5.6.4.5. I/O Timing Violation

6.5.6.4.6. Internal FPGA Path Timing Violation

Visible to Intel only — GUID: olj1606728958898

Ixiasoft

4.6.1.1.1. Generating the Synthesis Design Example

The make_qii_design.tcl generates a synthesizable hardware design example and an Quartus® Prime project, ready for compilation.

To generate synthesizable design example, run the following script at the end of IP generation:

quartus_sh -t make_qii_design.tcl

To specify an exact device to use, run the following script:

quartus_sh -t make_qii_design.tcl [device_name]

This script generates a qii directory containing a project called ed_synth.qpf. You can open and compile this project using the Quartus® Prime software.

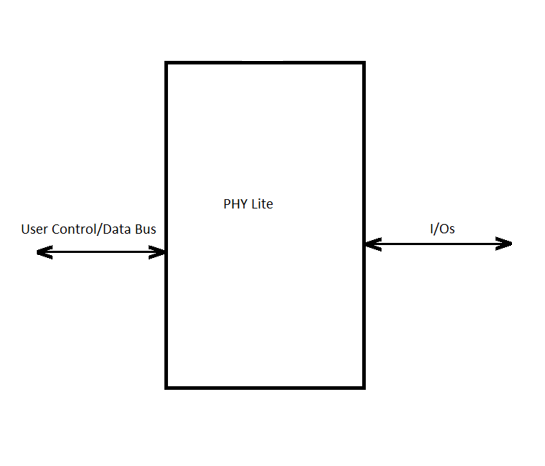

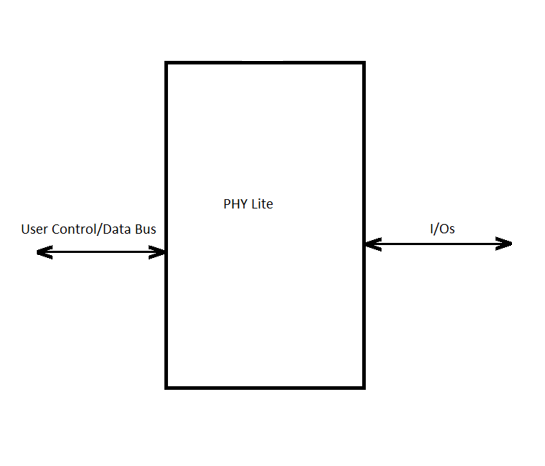

Figure 105. High-Level View of the Synthesis Design Example with One Group