Visible to Intel only — GUID: bhc1410942161162

Ixiasoft

1. About the PHY Lite for Parallel Interfaces IP

2. PHY Lite for Parallel Interfaces Intel Agilex FPGA IP

3. PHY Lite for Parallel Interfaces Intel Stratix 10 FPGA IP

4. PHY Lite for Parallel Interfaces Intel Arria 10 and Intel Cyclone 10 GX FPGA IPs

5. PHY Lite for Parallel Interfaces Intel® FPGA IP User Guide Document Archives

6. Document Revision History for the PHY Lite for Parallel Interfaces IP User Guide

3.5.6.4.1. Timing Closure: Dynamic Reconfiguration

3.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

3.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

3.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

3.5.6.4.5. I/O Timing Violation

3.5.6.4.6. Internal FPGA Path Timing Violation

4.5.6.4.1. Timing Closure: Dynamic Reconfiguration

4.5.6.4.2. Timing Closure: Input Strobe Setup and Hold Delay Constraints

4.5.6.4.3. Timing Closure: Output Strobe Setup and Hold Delay Constraints

4.5.6.4.4. Timing Closure: Non Edge-Aligned Input Data

4.5.6.4.5. I/O Timing Violation

4.5.6.4.6. Internal FPGA Path Timing Violation

Visible to Intel only — GUID: bhc1410942161162

Ixiasoft

4.7.1. Implementation using the PHY Lite for Parallel Interfaces IP

You can configure the PHY Lite for Parallel Interfaces IP to support multiple groups (maximum 48 I/O pins each).

The following lists the possible implementations:

- Instantiates one PHY Lite for Parallel Interfaces IP with two groups

- Bidirectional type for DQ and DQS signals

- Output type for Addr/Cmd signals

Note: Each group in the PHY Lite for Parallel Interfaces IP can have 48 I/Os, and the IP supports up to 18 groups.

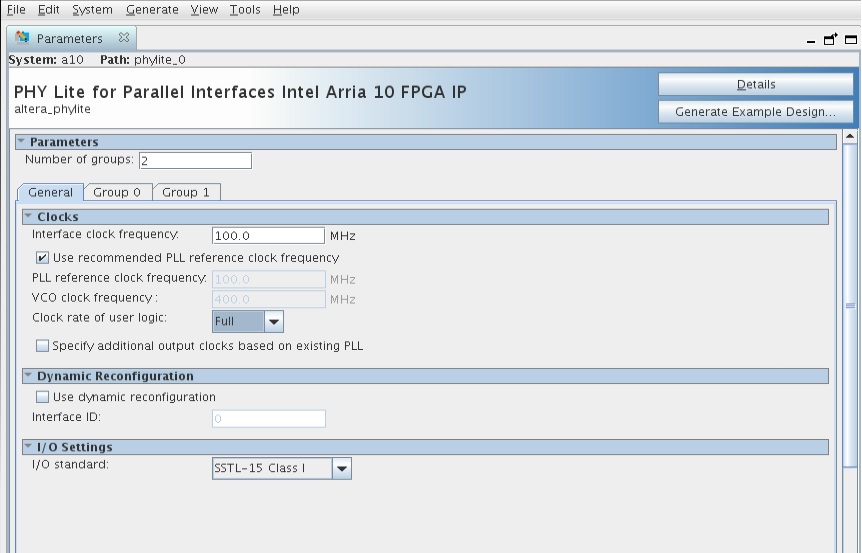

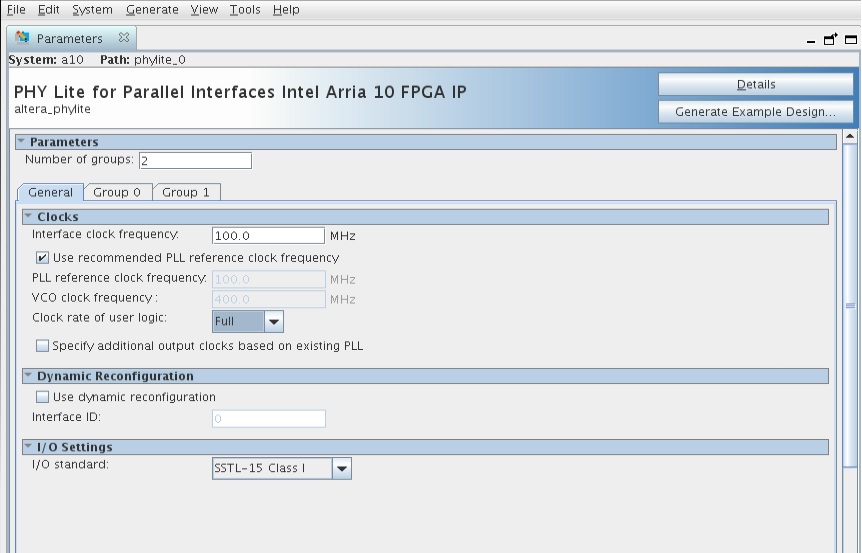

Figure 94. General Tab Settings

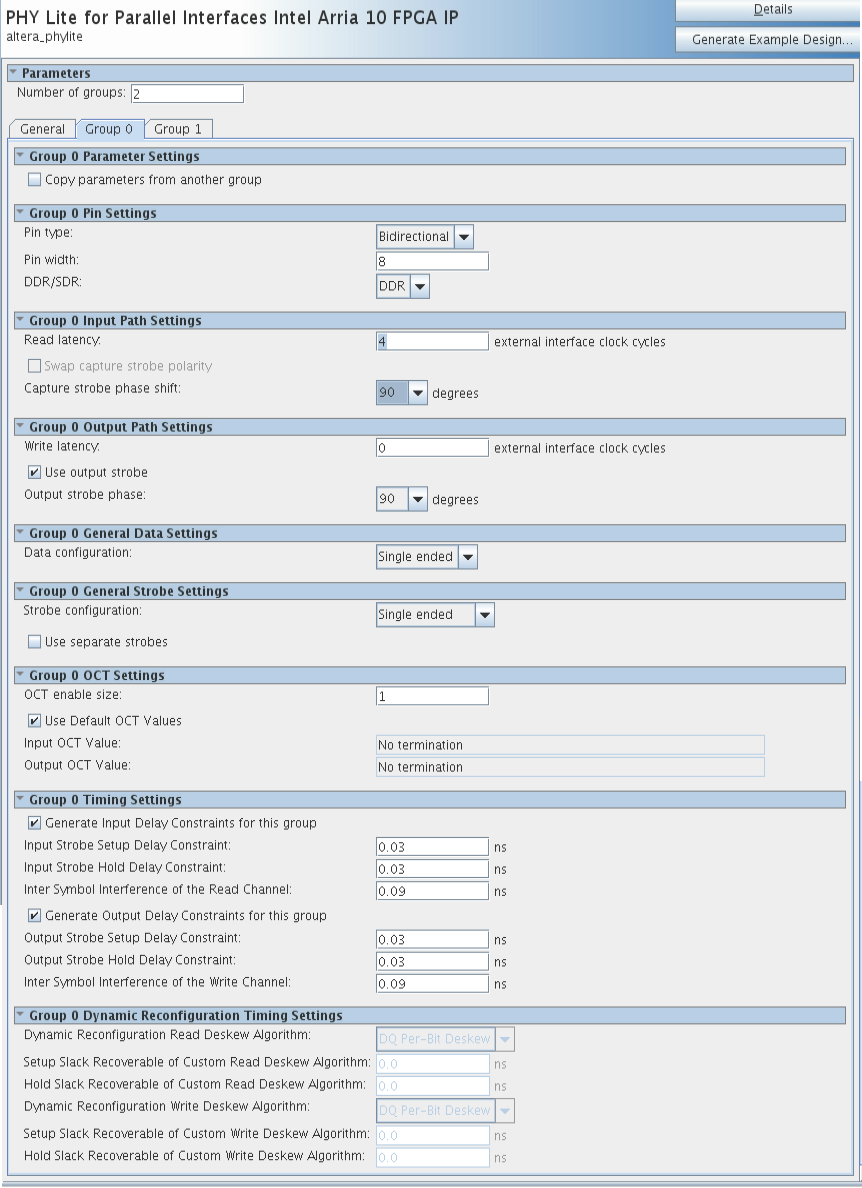

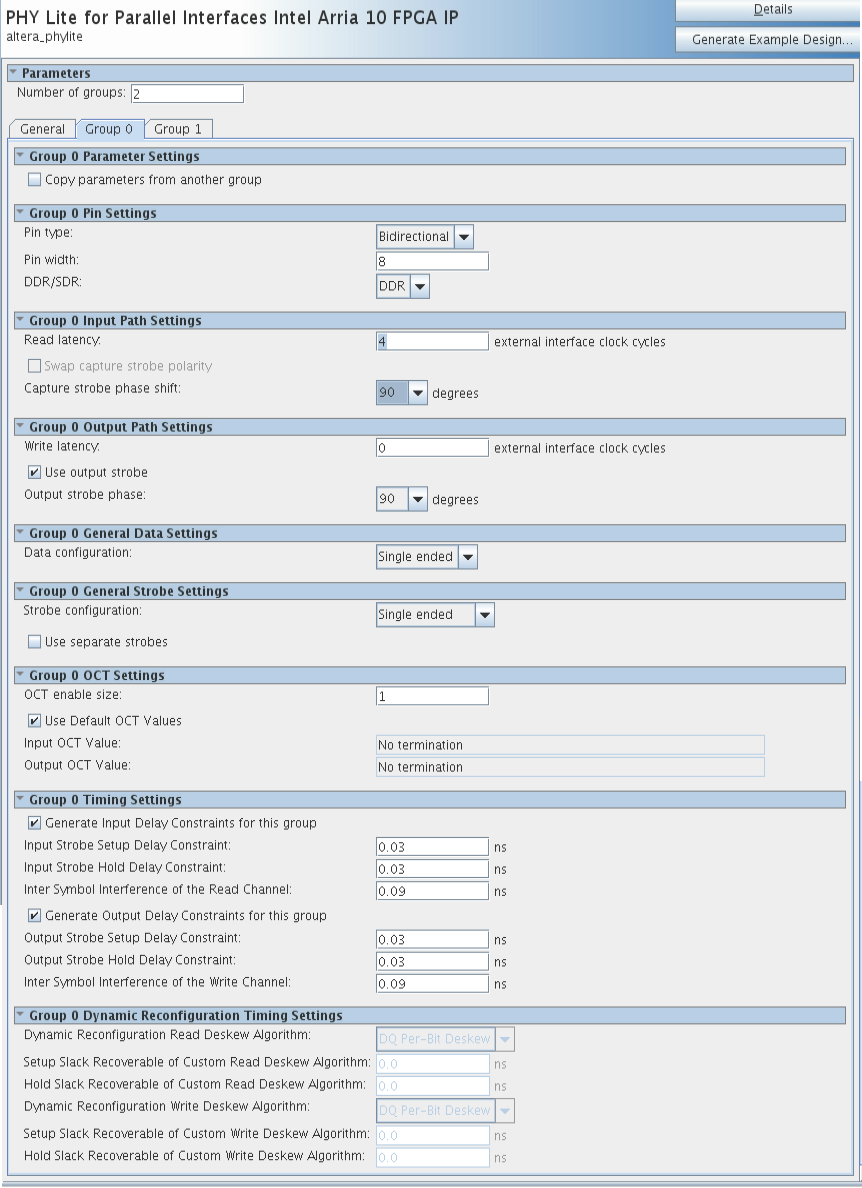

Figure 95. Group 0 settings (Bidirectional type for DQ and DQS)

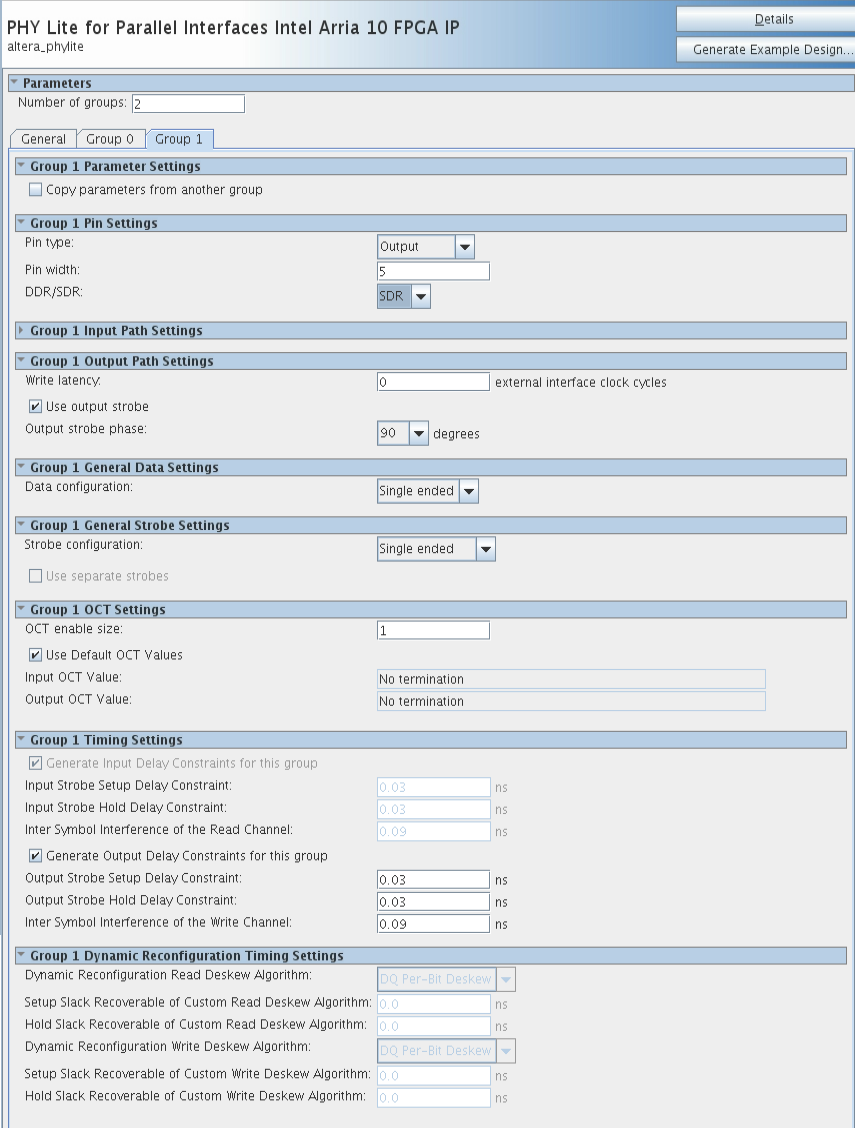

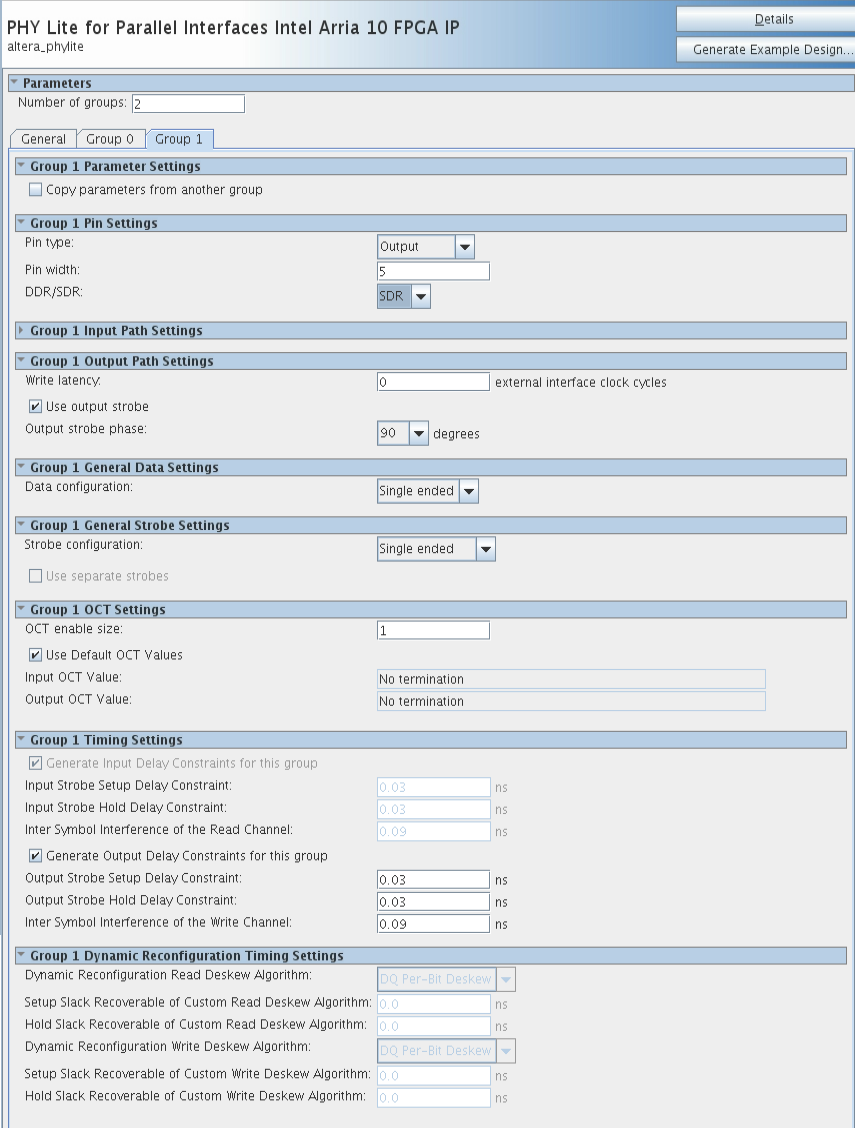

Figure 96. Group 1 settings (Output type for Addr/Cmd)