3.1. Design Example Parameters

Describes the F-Tile CPRI PHY IP Design Example Example Design and Analog Parameters tabs

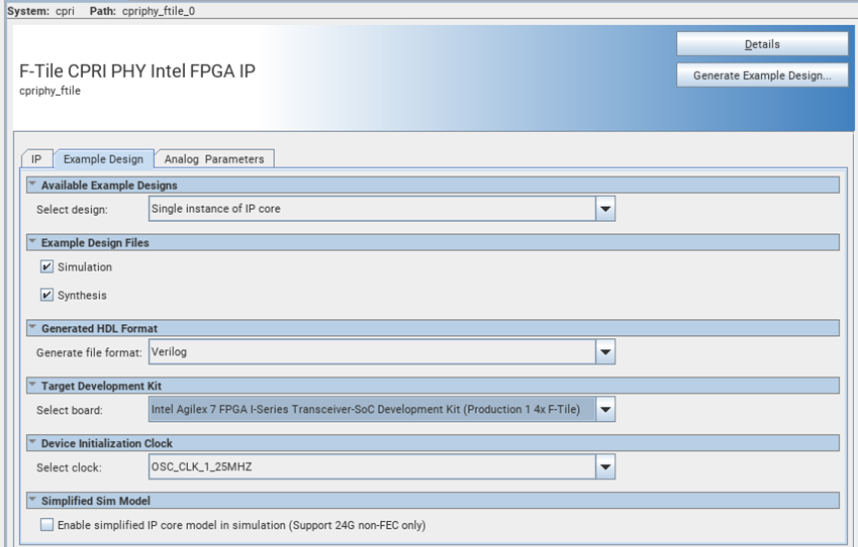

Example Design Tab

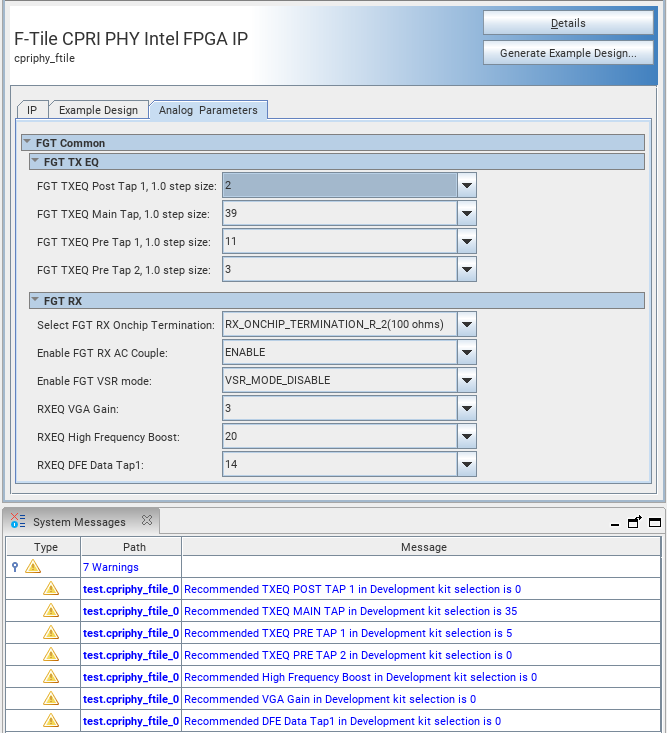

If you select Intel Agilex 7 FPGA I-Series Transceiver-SoC Development Kit for Target Development Kit, it only supports OSC_CLK_1_125MHZ for Device initialization clock. If you configure analog parameters other than the default and recommended values (Table 9), you see warnings to recommend you set to the default values.

Figure 6. Target Development Kit in the Example Design Tab

Figure 7. Warnings

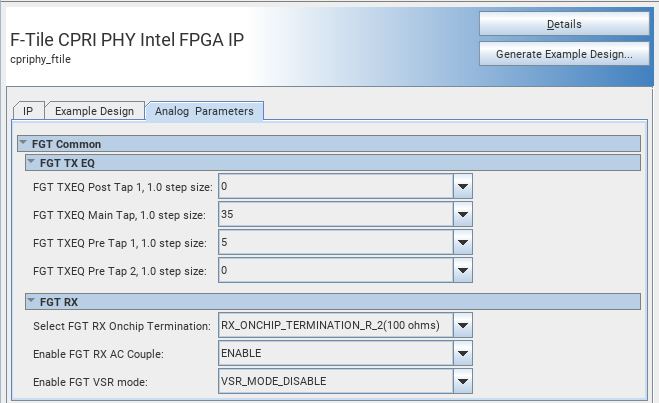

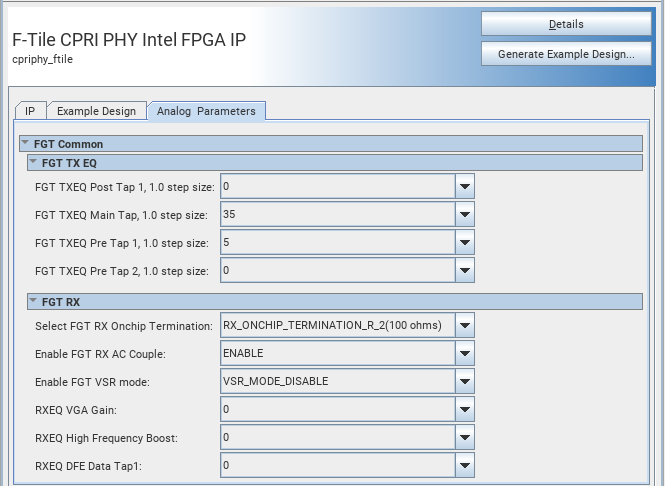

Analog Parameters Tab

For all parameters in the Analog Parameters tab, refer to the Analog Parameters for F-Tile IPs.

When the CPRI rate is 6.1440G and below, the GUI has three extra analog parameters to configure:

- RXEQ VGA Gain

- RXEQ High Frequency Boost

- RXEQ DFE Data Tap1

Figure 8. For CPRI Rates 9.8304G and Above

Figure 9. For CPRI Rates 6.1440G and Below

| Parameter | Value |

|---|---|

| FGT TXEQ Post Tap 1, 1.0 step size | 0 |

| FGT TXEQ Main Tap 1.0 step size | 35 |

| FGT TXEQ Pre Tap 1, 1.0 step size | 5 |

| FGT TXEQ Pre Tap 2, 1.0 step size | 0 |

| FGT RX Onchip Termination | RX_ONCHIP_TERMINATION_R_2 (100 ohms) |

| Enable FGT RX AC Couple | ENABLE |

| Enable FGT VSR mode |

|

| RXEQ VGA Gain | 0 (Required only when CPRI rate is 6.1440Gbps and below) |

| RXEQ High Frequency Boost | 0 (Required only when CPRI rate is 6.1440Gbps and below) |

| RXEQ DFE Data Tap1 | 0 (Required only when CPRI rate is 6.1440Gbps and below) |