Visible to Intel only — GUID: xai1706333370249

Ixiasoft

Visible to Intel only — GUID: xai1706333370249

Ixiasoft

1.5. Precompiled Component (PCC) Generation Flow

PCC generation reduces Synthesis compile time through the following steps and allows you to iterate and go to post-synthesis timing analysis stages faster and reduce the development cycle time:

- Synthesizes Intel® FPGA IP components in your design.

- Generates and caches IP compilation results in your project's ocs_cache_dir (IP cache) directory.

- Reuses the IP cache in subsequent Synthesis runs.

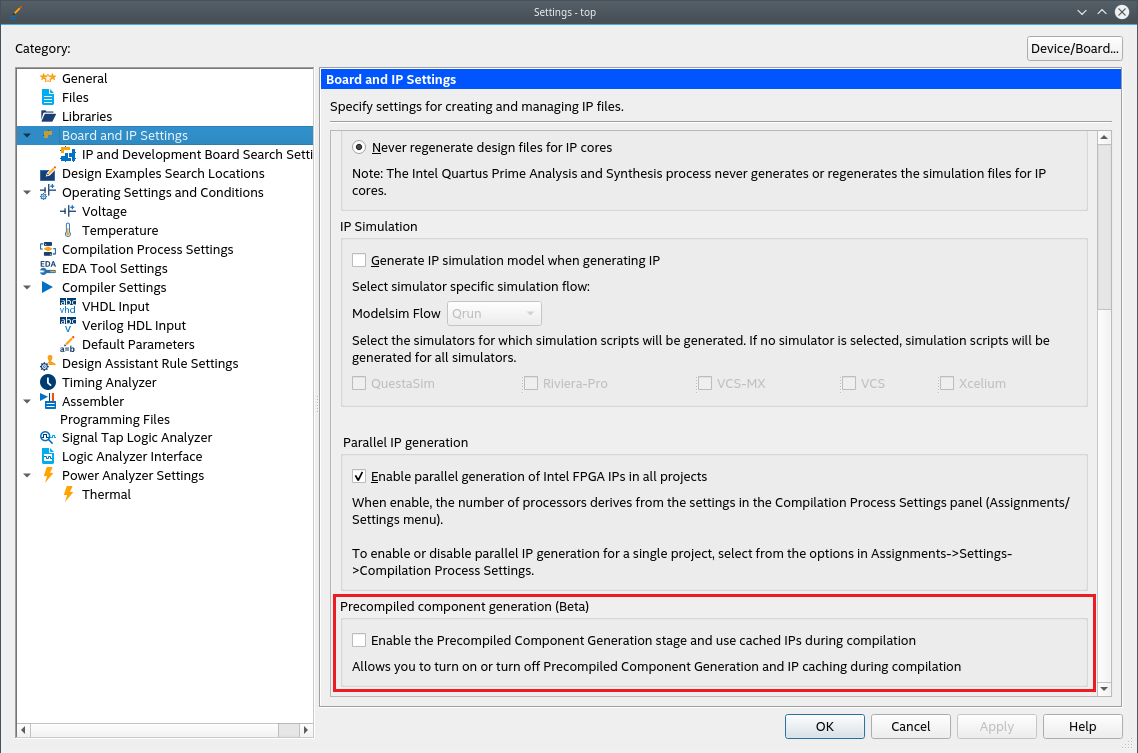

By default, the PCC generation flow is disabled. You can enable it from Assignments > Settings > Board and IP Settings dialog as shown in the following:

If the PCC generation flow compiles successfully, you can view the Precompiled Components compilation report for each IP that participates in the flow under the Compilation Reports dialog.

Advantages of PCC Generation Flow

- Each unique IP is generated only once and cached, so the subsequent Synthesis run does not perform PCC generation if you have not modified any IP in your design.

- If you modify any IP, the PCC generation flow synthesizes only that IP and skips synthesizing the remaining IPs.

- The PCC generation process occurs in parallel for each IP.

- Synthesis compile time savings scales with the proportion of the design that is IP.