Visible to Intel only — GUID: lzi1692369795357

Ixiasoft

Visible to Intel only — GUID: lzi1692369795357

Ixiasoft

1.6. Analysis & Elaboration Flow

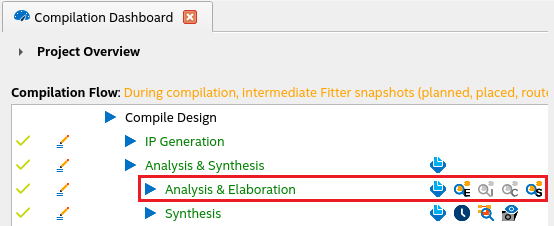

This flow allows you to access the preview modes of the Analysis & Elaboration stage, as shown in the following image:

The Analysis & Elaboration stage is composed of a series of checkpoints and you can preview your design at each checkpoint as shown in Analysis & Elaboration Checkpoints, where:

- Elaborated: Provides an unmodified preview of your design captured directly from RTL.

- Instrumented: Provides an instrumented preview with system-level debugging (debug fabric and Signal Tap logic analyzer inserted in your design). This checkpoint is disabled by default (Hint: See Note below to enable it).

- Constrained: Provides a design preview with SDC-on-RTL constraints shown on the target nodes. This checkpoint is disabled by default (Hint: See Note below to enable it).

- Swept: Provides a design preview with unnecessary logic removed from your design.

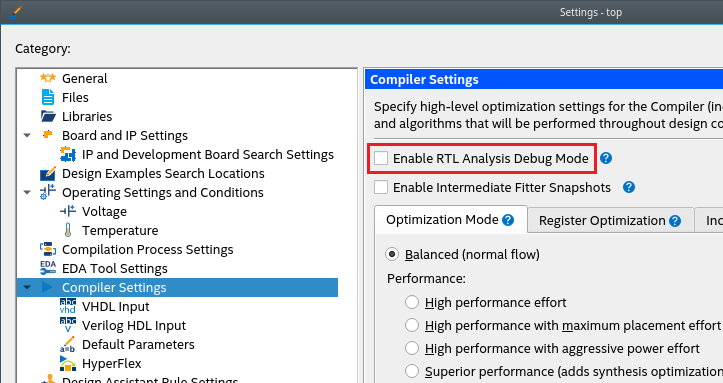

You can control the number of checkpoints generated using the RTL Analysis Debug Mode option under Project > Settings. This mode is off by default, which means only Elaborated and Swept checkpoints are available, and Instrumented and Constrained checkpoints are unavailable. When you enable this mode, all four checkpoints become available.

When the mode is off, you can obtain information about the Hierarchies Optimized Away and Top Causes for Logic Optimized Away During Sweep, under Synthesis Compilation Reports > Synthesis > Analysis & Elaboration.

For information about the Synthesis stage, refer to Design Synthesis.

A design compiled with the DNI-based compilation flow is not compatible with the Quartus® Prime software versions older than 23.3 due to the new DNI database. Ensure the following:

- If you compile your design with the software version 23.3 and launch the project in the Quartus® Prime software GUI, a message displays indicating that you compiled your design with a different compilation engine. If you continue to launch the project, then you must recompile the design. This also applies for designs compiled with the Quartus® Prime software versions older than 23.3.

- For any partition-based design (for example, Partial Reconfiguration), mixing 23.3 version with 23.2 or older version compilation flow among the user-defined partitions is not supported. You must compile all partitions with the same compilation flow.

- For version-compatible design export or import feature, a design compiled with and exported from an older Quartus® Prime version requires the Quartus® Prime 23.2 or older version. Similarly, the Quartus® Prime 23.3 version is necessary for version-compatible databases compiled with the DNI flow, and this feature is not supported yet.

Executing Tcl Commands

The Quartus® Prime software GUI (quartus) and Synthesis tool (quartus_syn) support Tcl commands.

Use one of the following suitable methods to execute your Tcl commands:

Quartus® Prime Software GUI (quartus)Perform the following steps in the GUI:

- On the Compilation Dashboard, run Analysis & Synthesis > Analysis & Elaboration task to generate the netlist.

- Click the magnifier icon to Invoke the RTL Analyzer.

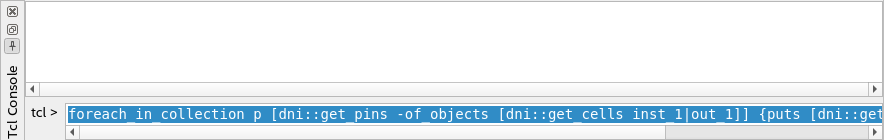

- Execute your Tcl command in the Tcl Console .

- Enable the flow for your project with the following command:

quartus_syn --analysis_and_elaboration <project_name>

- Load your design.

> quartus_syn -s <... Quartus Info Message...> tcl> project_open top tcl> dni::load_design -checkpoint elaborated dms_path::sandboxes::sandbox_1239_0::design

- Execute your Tcl commands:

tcl> foreach_in_collection p [dni::get_pins -of_objects [dni::get_cells inst_1|out_1]] {puts [dni::get_property -name name -object $p]} a[0] a[1] o tcl> foreach_in_collection p [dni::get_pins -of_objects [dni::get_cells inst_1|out_1]] {puts [dni::get_property -name direction -object $p]} input input output tcl>