Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: jbr1444415589919

Ixiasoft

Visible to Intel only — GUID: jbr1444415589919

Ixiasoft

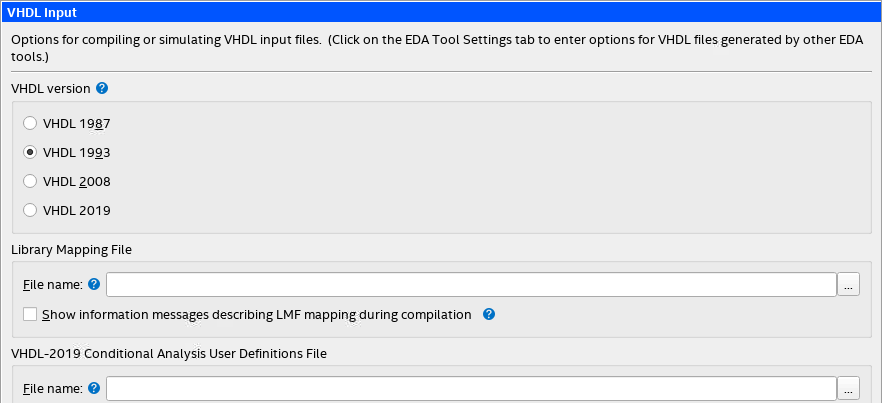

2.11.2.1. VHDL Input Settings (Settings Dialog Box)

| Setting |

Description |

|---|---|

| VHDL Version |

Specifies the VHDL standard for use during synthesis of VHDL input design files. Select the language standards that corresponds with the VHDL files. |

| Library Mapping File |

Specifies a Library Mapping File (.lmf) for use in synthesizing VHDL files that contain IP cores. Specify the full path name of the LMF in the File name box. |

| VHDL-2019 Conditional Analysis User Definitions File | Specifies the .ini file that contains your user-defined VHDL 2019 conditional analysis identifier-value pairs. |