Visible to Intel only — GUID: iga1457455222198

Ixiasoft

Visible to Intel only — GUID: iga1457455222198

Ixiasoft

38.6.1.1. Adding the EIC Interface Shadow Register Set

This section describes how to add the EIC interface and shadow register sets to a Nios® II processor core in Platform Designer, through the parameter editor interface.

- In Platform Designer, double-click the Nios® II processor to open the parameter editor interface.

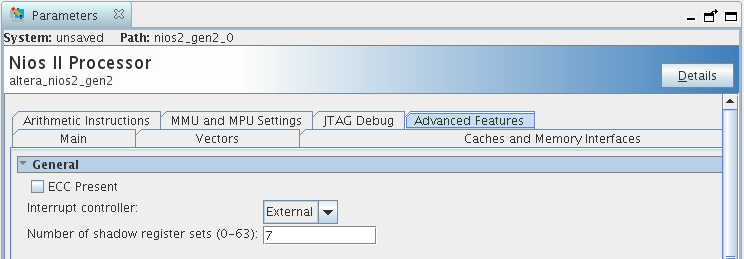

- Enable the EIC interface on the Nios® II processor by selecting it in the Interrupt Controller list in the Advanced Features tab, as shown in the figure below.

There are two options for Interrupt Controller: Internal and External. If you select Internal, the processor is implemented with the internal interrupt controller. Select External to implement the processor with an EIC interface.

Note: When you implement the EIC interface, you must connect an EIC, such as the VIC. Failure to connect an EIC results in a Platform Designer error. - Select the desired number of shadow register sets. In the Number of shadow register sets list, select the number of register sets that matches your system performance goals.

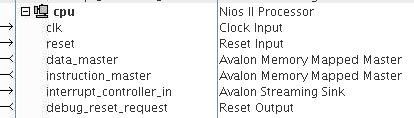

- Click Finish to exit from the Nios® II parameter editor interface . Notice that the processor shows an unconnected interrupt_controller_in Avalon® -ST sink, as shown in the figure below.

Shadow register sets reduce the context switching overhead associated with saving and restoring registers, which can otherwise be significant. If possible, add one shadow register set for each interrupt that requires high performance.