1.1. Functional Description for the Programmed Input/Output (PIO) Design Example

The PIO design example automatically creates the files necessary to simulate and compile in the Intel® Quartus® Prime software. The design example covers a wide range of parameters. However, it does not cover all possible parameterizations of the P-Tile Hard IP for PCIe.

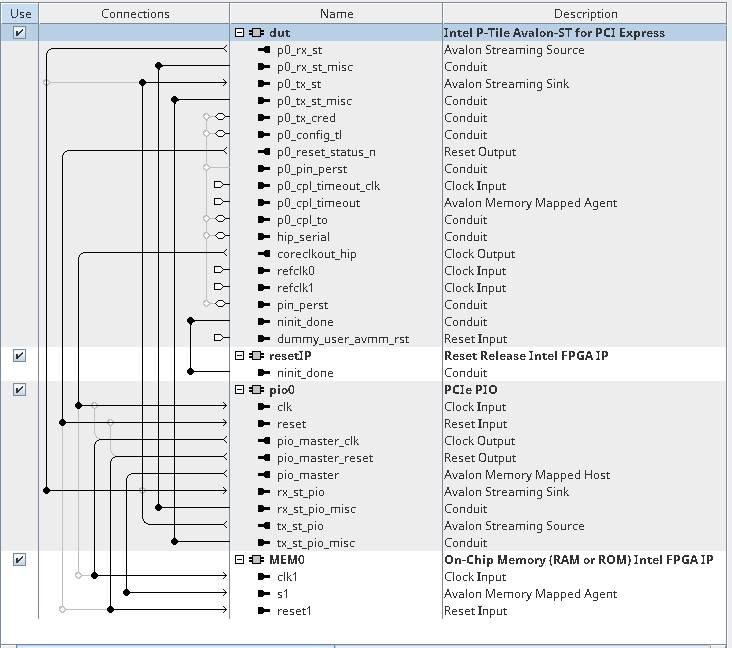

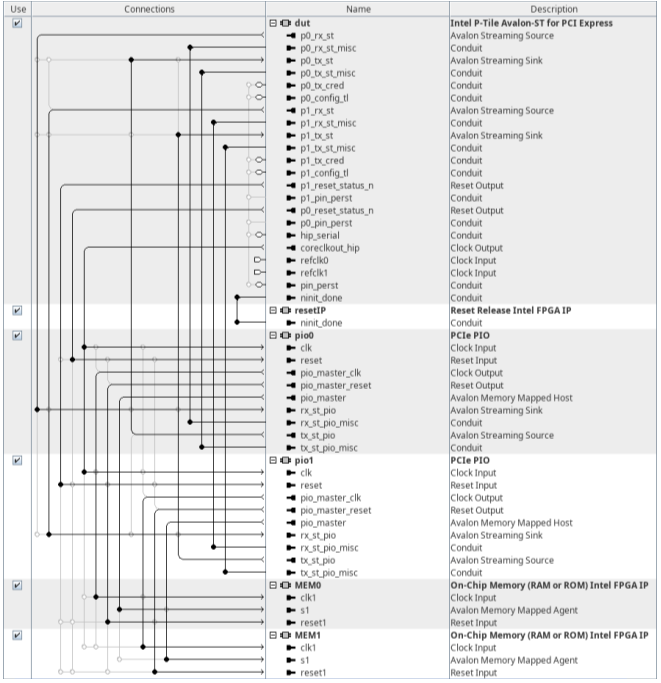

This design example includes the following components:

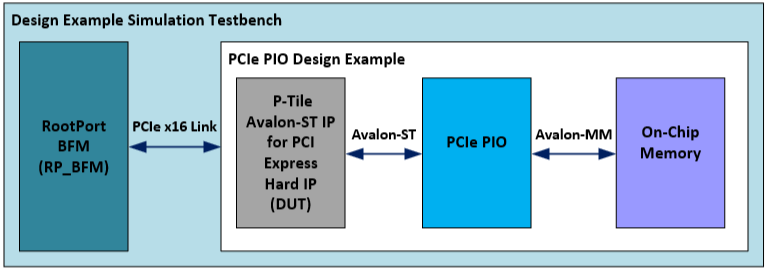

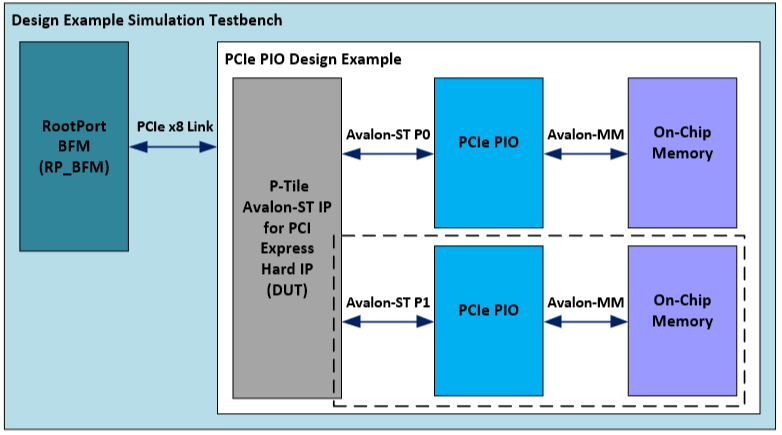

- The generated P-Tile Avalon Streaming Hard IP Endpoint variant (DUT) with the parameters you specified. This component drives TLP data received to the PIO application.

- The PIO Application (APPS) component, which performs the necessary translation between the PCI Express TLPs and simple Avalon-MM writes and reads to the on-chip memory.

- An on-chip memory (MEM) component. For the 1x16 design example, the on-chip memory consists of one 16 KB memory block. For the 2x8 design example, the on-chip memory consists of two 16 KB memory blocks.

- Reset Release IP: This IP holds the control circuit in reset until the device has fully entered user mode. The FPGA asserts the INIT_DONE output to signal that the device is in user mode. The Reset Release IP generates an inverted version of the internal INIT_DONE signal to create the nINIT_DONE output that you can use for your design.The nINIT_DONE signal is high until the entire device enters user mode. After nINIT_DONE asserts (low), all logic is in user mode and operates normally. You can use the nINIT_DONE signal in one of the following ways:

- To gate an external or internal reset.

- To gate the reset input to the transceiver and I/O PLLs.

- To gate the write enable of design blocks such as embedded memory blocks, state machine, and shift registers.

- To synchronously drive register reset input ports in your design.

The simulation testbench instantiates the PIO design example and a Root Port BFM to interface with the target Endpoint.

The test program writes to and reads back data from the same location in the on-chip memory. It compares the data read to the expected result. The test reports, "Simulation stopped due to successful completion" if no errors occur.

- Gen4 x16 Endpoint

- Gen3 x16 Endpoint

- Gen4 x8x8 Endpoint

- Gen3 x8x8 Endpoint