Product Features

IP Functionality

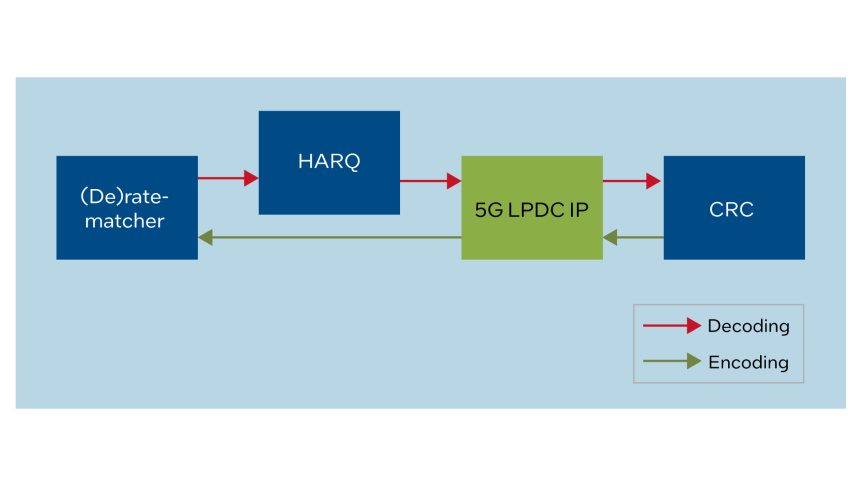

- Encode and decode supported

- CRC checker module (CRC24B without concatenation)

- Rate matcher

- Per-block modifiable code block length and code rate

- 5G LDPC-V Lite option for reduced resource usage

- Improved block-error rate (BLER) performance for high reliability signal-to-noise ratios (SNRs) for ultra-reliable low-latency communications (URLLC)

- Derate matcher

- By passable hybrid automatic repeat request (HARQ) block

- Code block segmentation CRC module (CRC24B without concatenation)

- Per-block modifiable code block length, code rate, and maximum number of iterations

- Configurable input precision

- Layered decoder scheduling architecture to double the speed of convergence compared to non-layered architecture

- Early termination based on the syndrome check using four layers or full syndrome after each iteration

Performance Specifications

- Complies with the 3GPP 5G LDPC specification

- No external memory requirement

User and System Interfaces

- Avalon®-Streaming (Avalon-ST) input and output interfaces

Debug and Test Capabilities

- Provides C and MATLAB bit-accurate models for performance simulation and RTL test vector generation

- Testbench and example design available