Visible to Intel only — GUID: xbh1730836392333

Ixiasoft

2.4. Dual Simplex Design Example

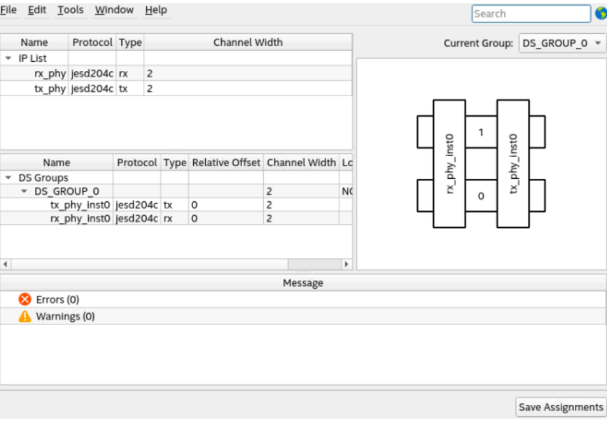

Figure 4. Dual Simplex Design Example Block Diagram

The Dual Simplex example design currently supports Duplex Case only with TX and RX in the same configuration. For more information, refer to the Dual Simplex Support section in the GTS JESD204C Intel® FPGA IP User Guide.

To generate the design example:

- Create a project targeting Agilex™ 5 device family and select the desired device.

- In the IP Catalog, Tools > IP Catalog, select GTS JESD204C Intel® FPGA IP . Modify the IP Tab for required JESD configurations. Current JESD IP supports same configuration for both TX and RX.

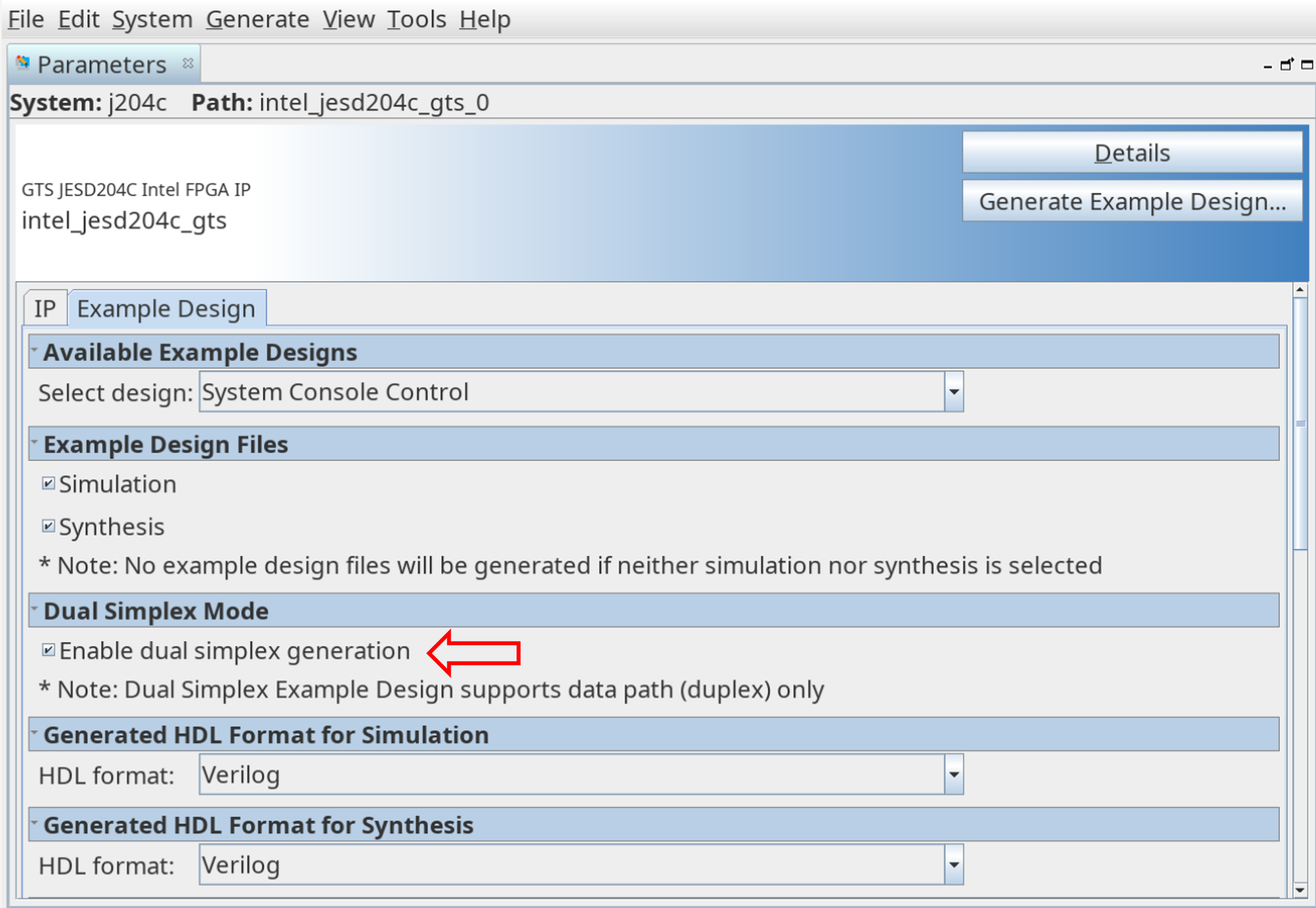

- In the GTS JESD204C Intel® FPGA IP GUI, go to the Example Design tab and enable Enable dual simplex generation.

- Generate the example design and after opening the example design, choose the Dual Simplex assignment editor in the Assignments menu.

- Verify the TX and RX PHY relative offsets. Save assignments and run IP generation in Quartus® Prime. This will generate the HSSI dual simplex generation.

Related Information