Visible to Intel only — GUID: yvw1645094148505

Ixiasoft

1. Agilex™ 5 General-Purpose I/O Overview

2. Agilex™ 5 HSIO Banks

3. Agilex™ 5 HVIO Banks

4. Agilex™ 5 HPS I/O Banks

5. Agilex™ 5 SDM I/O Banks

6. Agilex™ 5 I/O Troubleshooting Guidelines

7. GPIO Intel® FPGA IP

8. Programmable I/O Features Description

9. Document Revision History for the General-Purpose I/O User Guide: Agilex™ 5 FPGAs and SoCs

2.5.1. I/O Standard Placement Restrictions for True Differential I/Os

2.5.2. Placement Restrictions for True Differential and Single-Ended I/O Standards in the Same or Adjacent HSIO Bank

2.5.3. VREF Sources and Input Standards Grouping

2.5.4. HSIO Pin Restrictions for External Memory Interfaces

2.5.5. RZQ Pin Requirement

2.5.6. I/O Standards Implementation Based on VCCIO_PIO Voltages

2.5.7. I/O Standard Selection and I/O Bank Supply Compatibility Check

2.5.8. Simultaneous Switching Noise

2.5.9. HPS Shared I/O Requirements

2.5.10. Clocking Requirements

2.5.11. SDM Shared I/O Requirements

2.5.12. Unused Pins

2.5.13. VCCIO_PIO Supply for Unused HSIO Banks

2.5.14. HSIO Pins During Power Sequencing

2.5.15. Drive Strength Requirement for HSIO Input Pins

2.5.16. Maximum DC Current Restrictions

2.5.17. 1.05 V, 1.1 V, or 1.2 V I/O Interface Voltage Level Compatibility

2.5.18. Connection to True Differential Signaling Input Buffers During Device Reconfiguration

2.5.19. LVSTL700 I/O Standards Differential Pin Pair Requirements

2.5.20. Implementing a Pseudo Open Drain

2.5.21. Allowed Duration for Using RT OCT

2.5.22. Single-Ended Strobe Signal Differential Pin Pair Restriction

2.5.23. Implementing SLVS-400 or DPHY I/O Standard with 1.1 V VCCIO_PIO

7.1. Release Information for GPIO Intel® FPGA IP

7.2. Generating the GPIO Intel® FPGA IP

7.3. GPIO Intel® FPGA IP Parameter Settings

7.4. GPIO Intel® FPGA IP Interface Signals

7.5. GPIO Intel® FPGA IP Architecture

7.6. Verifying Resource Utilization and Design Performance

7.7. GPIO Intel® FPGA IP Timing

7.8. GPIO Intel® FPGA IP Design Examples

Visible to Intel only — GUID: yvw1645094148505

Ixiasoft

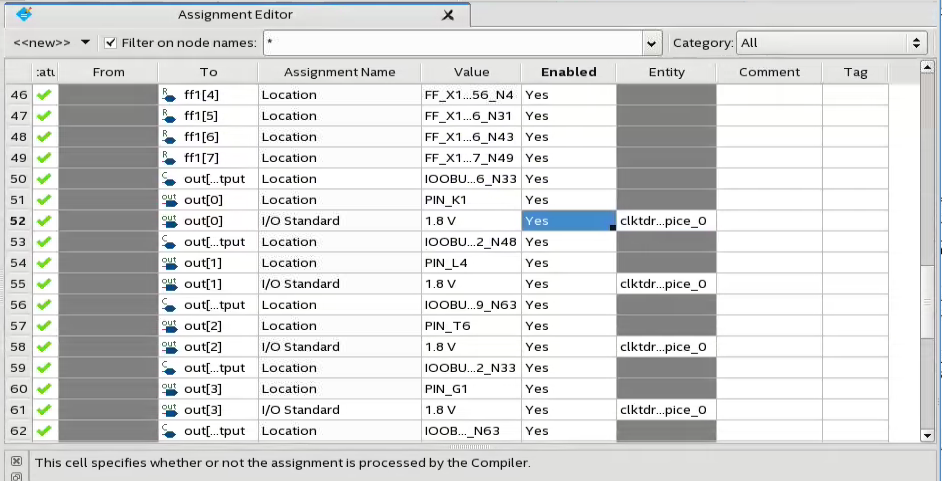

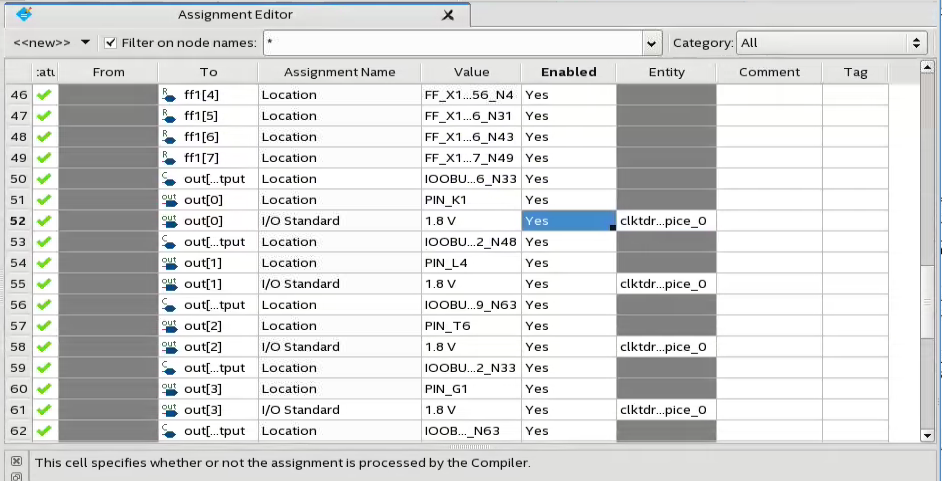

4.3.2. I/O Assignments with the Quartus® Prime Assignment Editor

You can assign all instance-specific settings and constraints through the Quartus® Prime Assignment Editor. You can filter assignments by node name or category.

Figure 32. Quartus® Prime Assignment Editor This figure shows an example of the user interface and does not represent actual components, features, or settings supported by Agilex™ 5 FPGAs.