Visible to Intel only — GUID: pko1678993615310

Ixiasoft

Visible to Intel only — GUID: pko1678993615310

Ixiasoft

6.2. Memory-to-Memory (M2M) Variant Design

The memory-to-memory (M2M) variant of the SoC design example illustrates a technique for embedded (SoC) Intel® FPGA AI Suite operations where the input data sets are primarily drawn from a memory or file sources. In this scenario, the data is typically not real time and is processed as fast as possible.

This design combines the HPS (Arm* Cortex*-A9) on the Intel® Arria® 10 SX SoC FPGA device with an additional DMA engine to allow for efficient transfer of data to and from the CPU and system memory.

In the M2M design, the source data originally resides within the host CPU domain on an SD card. The application uses the DMA controller to move the host-side data to the device side domain. This movement mimics the process that an application would typically do.

The test program then initiates Intel® FPGA AI Suite IP inference operations and wait for the IP to complete its process. Command-line options to the user application define how many inferences are executed.

After the inference operation is completed, the application uses the DMA to transfer the results back from external memory to the host domain. The results are then displayed on the Linux console.

The Intel modular scatter-gather direct memory access (mSGDMA) controller IP provides this DMA facility.

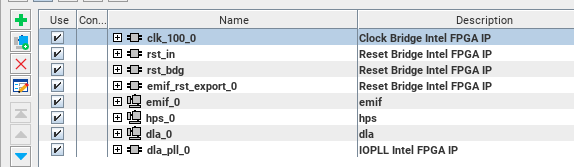

The M2M variant appears in Platform Designer as follows: