Visible to Intel only — GUID: jju1678993608357

Ixiasoft

1. Intel® FPGA AI Suite SoC Design Example User Guide

2. About the SoC Design Example

3. Intel® FPGA AI Suite SoC Design Example Quick Start Tutorial

4. Intel® FPGA AI Suite SoC Design Example Run Process

5. Intel® FPGA AI Suite SoC Design Example Build Process

6. Intel® FPGA AI Suite SoC Design Example Intel® Quartus® Prime System Architecture

7. Intel® FPGA AI Suite Soc Design Example Software Components

8. Streaming-to-Memory (S2M) Streaming Demonstration

A. Intel® FPGA AI Suite SoC Design Example User Guide Archives

B. Intel® FPGA AI Suite SoC Design Example User Guide Document Revision History

3.1. Initial Setup

3.2. Initializing a Work Directory

3.3. (Optional) Create an SD Card Image (.wic)

3.4. Writing the SD Card Image (.wic) to an SD Card

3.5. Preparing the Intel® Arria® 10 SX SoC FPGA Development Kit for the Intel® FPGA AI Suite SoC Design Example

3.6. Adding Compiled Graphs (AOT files) to the SD Card

3.7. Running the Demonstration Applications

3.5.1. Confirming Intel® Arria® 10 SX SoC FPGA Development Kit Board Settings

3.5.2. Connect the Intel® Arria® 10 SX SoC FPGA Development Kit to the Host Development System

3.5.3. Configuring the Intel® Arria® 10 SX SoC FPGA Development Kit UART Connection

3.5.4. Determining the Intel® Arria® 10 SX SoC FPGA Development Kit IP Address

7.1.1. Yocto Recipe: recipes-core/images/coredla-image.bb

7.1.2. Yocto Recipe: recipes-bsp/u-boot/u-boot-socfpga_%.bbapend

7.1.3. Yocto Recipe: recipes-drivers/msgdma-userio/msgdma-userio.bb

7.1.4. Yocto Recipe: recipes-drivers/uio-devices/uio-devices.bb

7.1.5. Yocto Recipe: recipes-kernel/linux/linux-socfpga-lts_5.15.bbappend

7.1.6. Yocto Recipe: wic

Visible to Intel only — GUID: jju1678993608357

Ixiasoft

3.5.1. Confirming Intel® Arria® 10 SX SoC FPGA Development Kit Board Settings

Confirm the board settings as follows:

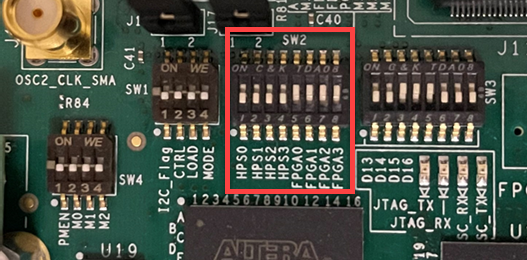

- Ensure that the Intel® Arria® 10 SX SoC FPGA Development Kit has the required DIP switch and jumper settings. The SoC example design requires that all DIP switches have their default settings except for SW2 switches 5, 6, 7, and 8, which should be switched ON:

For more details about default DIP switch and jumper settings, refer to Arria 10 SoC Development Kit User Guide .

- Ensure that the HILO cards are fitted correctly.

The Intel® Arria® 10 SX SoC FPGA Development Kit includes two DDR4 HILO cards: the HPS memory (1GB) and the FPGA memory (2GB). Both the HPS Memory and FPGA Memory DDR4 HILO modules must be fitted as shown in the following image: