Step 3: Allocating Placement and Routing Region for a PR Partition

For every base revision you create, the PR design flow places the corresponding persona core in your PR partition region. To locate and assign the PR region in the device floorplan for your base revision:

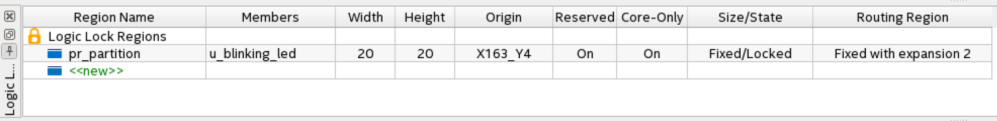

- Right-click the u_blinking_led instance in the Project Navigator and click . The region appears in the Logic Lock Regions Window.

- Edit the Logic Lock Region name in the Logic Lock Regions Window by double-clicking the name. For this reference design, rename the Logic Lock Region to pr_partition.

- In the Logic Lock Regions window, specify the placement region co-ordinates in the Origin column. The origin corresponds to the lower-left corner of the region. For example, to set a placement region with (X1 Y1) co-ordinates as (163 4), specify the Origin as X163_Y4. The Intel® Quartus® Prime software automatically calculates the (X2 Y2) co-ordinates (top-right) for the placement region, based on the height and width you specify.

Note: This tutorial uses the (X1 Y1) co-ordinates - (163 4), and a height and width of 20 for the placement region. Define any value for the placement region. Ensure that the region covers the blinking_led logic.

- Enable the Reserved and Core-Only options.

- Double-click the Routing Region option. The Logic Lock Routing Region Settings dialog box appears.

- Select Fixed with expansion for the Routing type. Selecting this option automatically assigns an expansion length of 2.

Note: The routing region must be larger than the placement region, to provide extra flexibility for the Fitter when the engine routes different personas.Figure 4. Logic Lock Regions Window

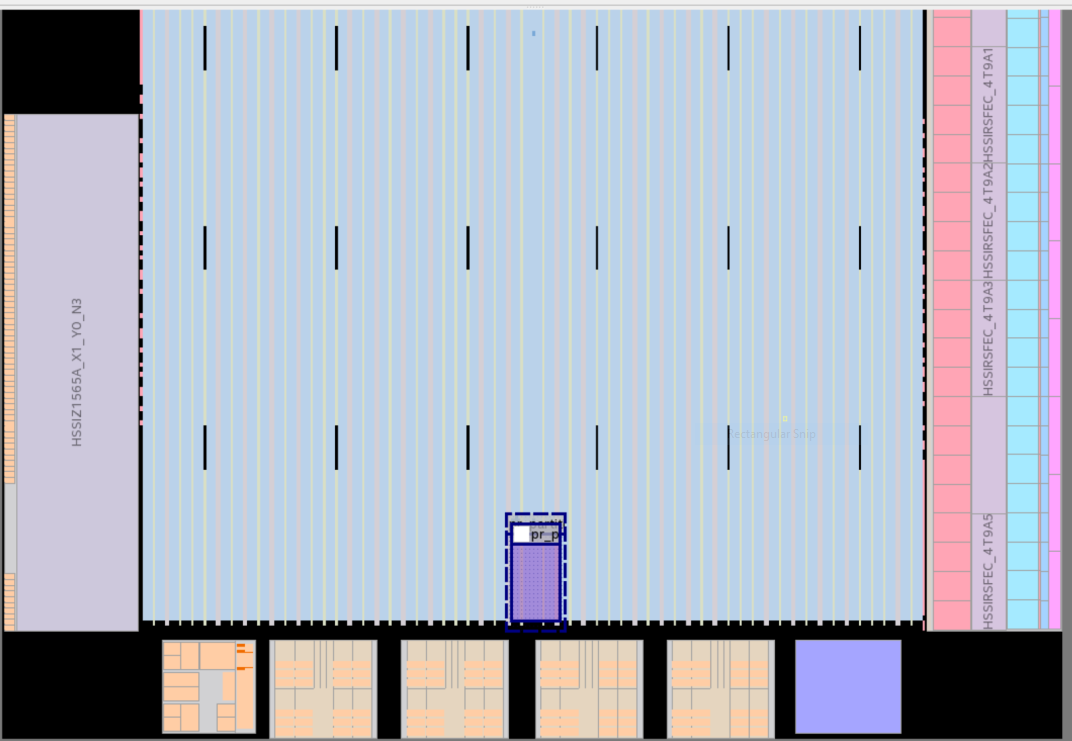

- Your placement region must enclose the blinking_led logic. Select the placement region by locating the node in Chip Planner. Right-click the pr_partition region name in the Logic Lock Regions Window and click .

The pr_partition region is color-coded.

Figure 5. Chip Planner Node Location

set_instance_assignment -name PLACE_REGION "X163 Y4 X182 Y23" -to \

u_blinking_led

set_instance_assignment -name RESERVE_PLACE_REGION ON -to \

u_blinking_led

set_instance_assignment -name CORE_ONLY_PLACE_REGION ON -to \

u_blinking_led

set_instance_assignment -name ROUTE_REGION "X161 Y2 X184 Y25" -to \

u_blinking_led