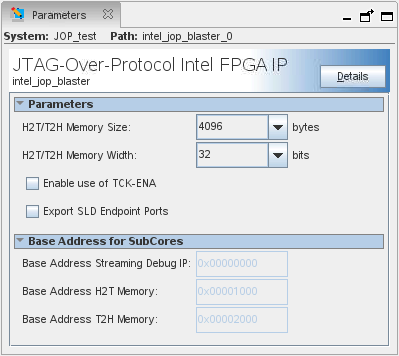

2. JTAG-Over-Protocol Intel® FPGA IP Parameters

The JTAG-Over-Protocol (JOP) Intel® FPGA IP is available in the Intel® Quartus® Prime Pro Edition IP Catalog: .

| Parameter | Description |

|---|---|

| H2T/T2H Memory Size | Sets the depth of memories in the JOP IP. |

| H2T/T2H Memory Width | Sets the width of the memories in the JOP IP. For 64-bit machines, set this parameter to 64 to avoid bus errors when you use the reference software. |

| Enable use of TCK-ENA | When this option is not enabled, the TCK frequency is generated by gating the input clock of the JOP IP. Closing with timing with a gated clock can cause challenges. Enable this option to help close timing if you are having problems. However, not all JTAG-based logic works with this option enabled. |

| Export SLD Endpoints | Enable to this option to export the following generated JTAG control signals:

Enabling this option stops connections between the JOP IP and the JTAG based logic that are made by Quartus synthesis. |

- Clock signal

- Reset signal

- Avalon® memory-mapped interface agent interface

The Avalon® memory-mapped interface interface data width is determined by the H2T/T2H Memory Width parameter of the JOP IP.

Run the JTAG-Over-Protocol IP on a clock signal operating at 100 MHz or lower.