Visible to Intel only — GUID: kjw1694053642789

Ixiasoft

Visible to Intel only — GUID: kjw1694053642789

Ixiasoft

4.9.1.2. Software Design Flow

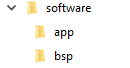

This section provides the design flow to generate and build the Nios V processor software project. To ensure a streamlined build flow, you are encouraged to create similar directory tree in your design project. The following software design flow is based on this directory tree.

To create the software project directory tree, follow these steps:

1. In your design project folder, create a folder called software.

2. In the software folder, create two folders called app and bsp.

Creating the Application BSP Project

To launch the BSP Editor, follow these steps:

- In the Platform Designer window, select File > New BSP. The Create New BSP windows appears.

- For BSP setting file, navigate to the software/bsp folder and name the BSP as settings.bsp.

BSP path: <project directory>/software/bsp/settings.bsp

- For System file (qsys or sopcinfo), select the Nios® V/g processor Platform Designer system (.qsys) file.

Note: For Quartus® Prime Standard Edition software, generate the BSP files using SOPCINFO. Refer to AN 980: Nios® V Processor Quartus® Prime Software Support for more information.

- For Quartus project, select the Quartus® Prime Project File.

- For Revision, select the correct revision.

- For CPU name, select the Nios® V/g processor.

- Select the Operating system as Altera HAL.

- Click Create to create the BSP file.

Figure 152. Create New BSP Window

Configuring the BSP Editor and Generating the BSP Project

- Go to Main > Settings > Advanced > hal.linker.

- Enable allow_code_at_reset only.

Figure 153. hal.linker Settings

- Click the BSP Linker Script tab in the BSP Editor

- In the Linker Section Name perform the following settings:

- Set .text and .exceptions to Instruction TCM1.

- Set the remaining Linker Section Name to the Data TCM1.

Figure 154. Linker Region Settings for TCM

- Click Generate BSP. Make sure the BSP generation is successful.

- Close the BSP Editor

Generating the Application Project File

- Navigate to the software/app folder and create your user application source code.

- Launch the Nios V Command Shell.

- Execute the command below to generate the user application CMakeLists.txt.

niosv-app --app-dir=software/app --bsp-dir=software/bsp \

--srcs=software/app/<user application>

Building the Application Project

You can choose to build the application project using RiscFree* IDE for Intel FPGAs or through the command line interface (CLI).

If you prefer using CLI, you can build the application using the following command:

cmake -G "Unix Makefiles" -B software/app/build -S software/app

make -C software/app/buildThe user application (.elf) file is created in software/app/build folder.

Generating the HEX File

You must generate a .hex file from your application .elf file, so you can create a .jic file suitable for programming flash devices.

- Launch the Nios V Command Shell.

- For Nios® V processor application boot from TCM, use the following command line to convert the ELF to HEX for your application. This command creates the user application (itcm.hex and dtcm.hex) file.

elf2hex software/app/build/<user_application>.elf -o itcm.hex \ -b <base address of ITCM> -w 32 \ -e <end address of ITCM> -r 4 elf2hex software/app/build/<user_application>.elf -o dtcm.hex \ -b <base address of DTCM> -w 32 \ -e <end address of DTCM> -r 4Note: If you enable ECC in Nios® V processor (thus, enabling ECC in TCM), use the following command line to convert the ELF to HEX for your application. This command line creates the user application (itcm.hex and dtcm.hex) files with ECC parity bits.elf2hex software/app/build/<user_application>.elf -o itcm.hex \ -b <base address of ITCM> -w 39 \ -e <end address of ITCM> -r 4 elf2hex software/app/build/<user_application>.elf -o dtcm.hex \ -b <base address of DTCM> -w 39 \ -e <end address of DTCM> -r 4

- Recompile the hardware design to memory-initialize both the HEX files into the Instruction TCM and Data TCM.