Visible to Intel only — GUID: izi1638888032251

Ixiasoft

1. About the Nios® V Embedded Processor

2. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Software and Platform Designer

3. Nios® V Processor Software System Design

4. Nios® V Processor Configuration and Booting Solutions

5. Nios® V Processor - Using the MicroC/TCP-IP Stack

6. Nios® V Processor Debugging, Verifying, and Simulating

7. Nios® V Processor — Remote System Update

8. Nios® V Processor — Using Custom Instruction

9. Nios® V Embedded Processor Design Handbook Archives

10. Document Revision History for the Nios® V Embedded Processor Design Handbook

4.1. Introduction

4.2. Linking Applications

4.3. Nios® V Processor Booting Methods

4.4. Introduction to Nios® V Processor Booting Methods

4.5. Nios® V Processor Booting from Configuration QSPI Flash

4.6. Nios V Processor Booting from On-Chip Memory (OCRAM)

4.7. Summary of Nios® V Processor Vector Configuration and BSP Settings

6.4.1. Prerequisites

6.4.2. Setting Up and Generating Your Simulation Environment in Platform Designer

6.4.3. Creating Nios V Processor Software

6.4.4. Generating Memory Initialization File

6.4.5. Generating System Simulation Files

6.4.6. Running Simulation in the QuestaSim Simulator Using Command Line

Visible to Intel only — GUID: izi1638888032251

Ixiasoft

4.5.1.3. GSFI Bootloader Example Design

Note: For Intel® Quartus® Prime Standard Edition software, refer to the topic Intel® Quartus® Prime Software Support to generate the example design.

You can download the GSFI bootloader example design from the Intel® FPGA Design Store. The example design is based on the Intel Arria 10 SoC Development Kit. Using the provided scripts, the hardware and software design are generated, and programmed respectively as SRAM Object Files (.sof) and JTAG Indirect Configuration Files (.jic) into the device.

Follow the steps below to generate the GSFI bootloader example design:

- Go to Intel® FPGA Design Store.

- Search for Arria10 - Bootloader GSFI Design package.

- Click on the link at the title.

- Accept the Software License Agreement.

- Download the package according to the Intel® Quartus® Prime software version of your host machine.

- Double-click to run the top.par file.

- top_project folder is created by default after running the PAR file.

- Open the top_project and refer to the readme.txt for how-to guide.

| File | Description |

|---|---|

| hw/ | Contains files necessary to run the hardware project. |

| ready_to_test/ | Contains pre-built hardware and software binaries to run the design on the target hardware. For this package, the target hardware is Intel® Arria® 10 SoC development kit. |

| scripts/ | Consists of scripts to build the design. |

| sw/ | Contains software application files. |

| readme.txt | Contains description and steps to apply the pre-bulit binaries or rebuild the binaries from scratch. |

Figure 44. GSFI Bootloader Example Design

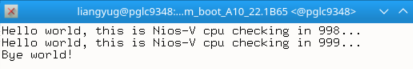

Figure 45. JUART Terminal Output

- In the beginning, the window displays the following message:

- Reaching the end, the window displays the following message: