Visible to Intel only — GUID: aec1660773532979

Ixiasoft

1. Quick Start Guide

2. Detailed Description for CPRI Multirate Design Example

3. Detailed Description for Ethernet Multirate Design Example

4. Detailed Description for Ethernet Multirate Design Example with Enabled Auto-Negotiation and Link Training

5. Detailed Description for PMA/FEC Direct PHY Multirate Design Example

6. Detailed Description for Ethernet to CPRI Design Example

7. F-Tile Dynamic Reconfiguration Design Example User Guide Archives

8. Document Revision History for the F-Tile Dynamic Reconfiguration Design Example User Guide

Visible to Intel only — GUID: aec1660773532979

Ixiasoft

1.2.4. Ethernet to CPRI Design Example Parameters

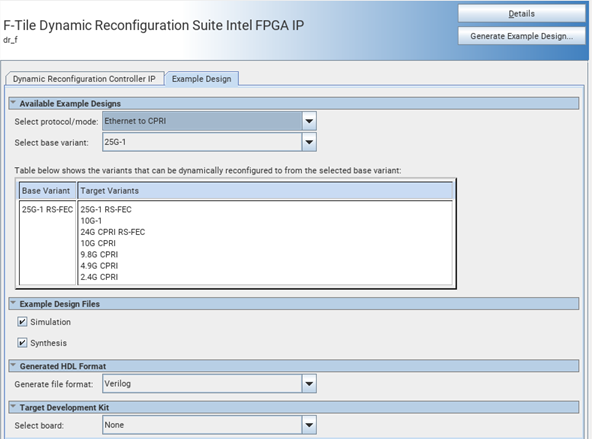

Figure 6. Ethernet to CPRI Example Design Tab

| Parameters | Value | Description |

|---|---|---|

| Select Protocol/mode | Ethernet to CPRI |

Select the IP protocol for dynamic reconfiguration. |

| Select Base Variant | 25G-1 25G-1 (with 1GE) |

Select the configuration of base variant for dynamic reconfiguration. |

| Example Design Files | Simulation Synthesis |

Simulation option generates the testbench and compilation-only project. Synthesis option generates the hardware design example. |

| Generated File Format | Verilog VHDL |

Select the HDL files format. If you select VHDL, you must simulate the testbench with a mixed-language simulator. |

| Target Development Kit | None Intel Agilex® 7 I-Series Transceiver-SoC Development Kit DK-SI-AGI027FA Intel Agilex® 7 I-Series Transceiver-SoC Development Kit DK-SI-AGI027FB |

Target development kit option specifies the target development kit used to generate the project. |