A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: ngq1620317208425

Ixiasoft

1. Introduction

2. FPGA Configuration First Mode

3. HPS Boot First Mode

4. Creating the Configuration Files

5. Golden System Reference Design and Design Examples

6. Configuring the FPGA Fabric from HPS Software

7. Debugging the Intel® Stratix® 10 SoC FPGA Boot Flow

8. Intel® Stratix® 10 SoC FPGA Boot User Guide Archives

9. Document Revision History for Intel® Stratix® 10 SoC FPGA Boot User Guide

Visible to Intel only — GUID: ngq1620317208425

Ixiasoft

4.7.1.2. Creating Configuration Files Using Graphical Interface

The following example creates the AVST configuration files for FPGA first mode using the Programming File Generator in GUI mode:

- Start the Programming File Generator in GUI mode by running the qpfgw command.

- Select the Device Family to be Intel® Stratix® 10.

- Select the Configuration mode to be AVST x8, AVST x16 or AVST x32.

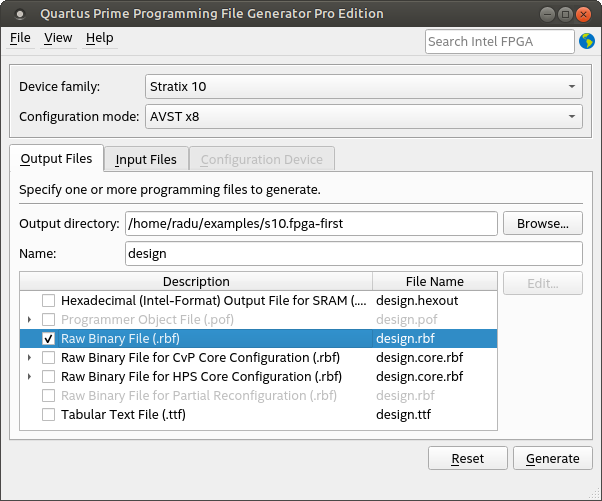

- In the Output Files tab:

- Change the output file Name to “design”.

- Check Raw Binary File (.rbf) option – the others are grayed out.

The Intel® Quartus® Prime Programming File Generator window is displayed:Figure 22. Intel® Quartus® Prime Programming File Generator Pro Edition Window: Output Files

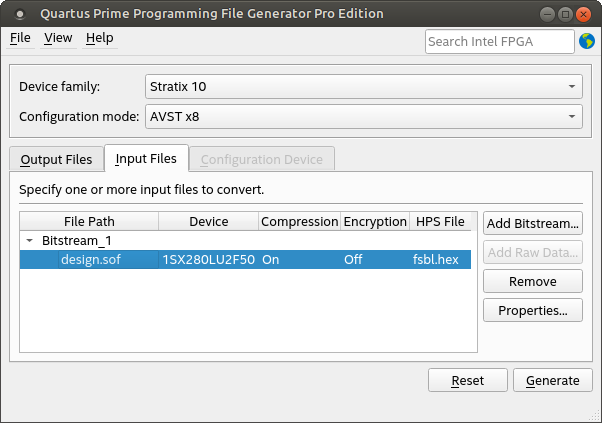

- Switch to Input Files tab by clicking it. In the Input Files tab, do the following:

- Click the Add Bitstream button, browse to your SOF file, then click Open.

- Click the newly added design.sof file, then click Properties. In the HPS settings > Bootloader section, click the “..” browse button, go to the location of your HPS FSBL hex file, select it and click Open.

The Intel® Quartus® Prime Programming File Generator window is displayed:Figure 23. Intel® Quartus® Prime Programming File Generator Pro Edition Window: Input Files

- Click the Generate button. Once the files are generated, a confirmation message is received.

- Optionally, go to File > Save or File > Save As to save the configuration in a .pfg file. You can generate the output again by applying the same options by running the command line version of the tool like this: quartus_pfg -c <filename.pfg>.