Visible to Intel only — GUID: bos1493517947427

Ixiasoft

1. Functional Description—UniPHY

2. Functional Description— Intel® MAX® 10 EMIF IP

3. Functional Description—Hard Memory Interface

4. Functional Description—HPS Memory Controller

5. Functional Description—HPC II Controller

6. Functional Description—QDR II Controller

7. Functional Description—RLDRAM II Controller

8. Functional Description—RLDRAM 3 PHY-Only IP

9. Functional Description—Example Designs

10. Introduction to UniPHY IP

11. Latency for UniPHY IP

12. Timing Diagrams for UniPHY IP

13. External Memory Interface Debug Toolkit

14. Upgrading to UniPHY-based Controllers from ALTMEMPHY-based Controllers

1.1. I/O Pads

1.2. Reset and Clock Generation

1.3. Dedicated Clock Networks

1.4. Address and Command Datapath

1.5. Write Datapath

1.6. Read Datapath

1.7. Sequencer

1.8. Shadow Registers

1.9. UniPHY Interfaces

1.10. UniPHY Signals

1.11. PHY-to-Controller Interfaces

1.12. Using a Custom Controller

1.13. AFI 3.0 Specification

1.14. Register Maps

1.15. Ping Pong PHY

1.16. Efficiency Monitor and Protocol Checker

1.17. UniPHY Calibration Stages

1.18. Document Revision History

1.7.1.1. Nios® II-based Sequencer Function

1.7.1.2. Nios® II-based Sequencer Architecture

1.7.1.3. Nios® II-based Sequencer SCC Manager

1.7.1.4. Nios® II-based Sequencer RW Manager

1.7.1.5. Nios® II-based Sequencer PHY Manager

1.7.1.6. Nios® II-based Sequencer Data Manager

1.7.1.7. Nios® II-based Sequencer Tracking Manager

1.7.1.8. Nios® II-based Sequencer Processor

1.7.1.9. Nios® II-based Sequencer Calibration and Diagnostics

1.17.1. Calibration Overview

1.17.2. Calibration Stages

1.17.3. Memory Initialization

1.17.4. Stage 1: Read Calibration Part One—DQS Enable Calibration and DQ/DQS Centering

1.17.5. Stage 2: Write Calibration Part One

1.17.6. Stage 3: Write Calibration Part Two—DQ/DQS Centering

1.17.7. Stage 4: Read Calibration Part Two—Read Latency Minimization

1.17.8. Calibration Signals

1.17.9. Calibration Time

4.1. Features of the SDRAM Controller Subsystem

4.2. SDRAM Controller Subsystem Block Diagram

4.3. SDRAM Controller Memory Options

4.4. SDRAM Controller Subsystem Interfaces

4.5. Memory Controller Architecture

4.6. Functional Description of the SDRAM Controller Subsystem

4.7. SDRAM Power Management

4.8. DDR PHY

4.9. Clocks

4.10. Resets

4.11. Port Mappings

4.12. Initialization

4.13. SDRAM Controller Subsystem Programming Model

4.14. Debugging HPS SDRAM in the Preloader

4.15. SDRAM Controller Address Map and Register Definitions

4.16. Document Revision History

10.7.1. DDR2, DDR3, and LPDDR2 Resource Utilization in Arria V Devices

10.7.2. DDR2 and DDR3 Resource Utilization in Arria II GZ Devices

10.7.3. DDR2 and DDR3 Resource Utilization in Stratix III Devices

10.7.4. DDR2 and DDR3 Resource Utilization in Stratix IV Devices

10.7.5. DDR2 and DDR3 Resource Utilization in Arria V GZ and Stratix V Devices

10.7.6. QDR II and QDR II+ Resource Utilization in Arria V Devices

10.7.7. QDR II and QDR II+ Resource Utilization in Arria II GX Devices

10.7.8. QDR II and QDR II+ Resource Utilization in Arria II GZ, Arria V GZ, Stratix III, Stratix IV, and Stratix V Devices

10.7.9. RLDRAM II Resource Utilization in Arria® V Devices

10.7.10. RLDRAM II Resource Utilization in Arria® II GZ, Arria® V GZ, Stratix® III, Stratix® IV, and Stratix® V Devices

13.1. User Interface

13.2. Setup and Use

13.3. Operational Considerations

13.4. Troubleshooting

13.5. Debug Report for Arria V and Cyclone V SoC Devices

13.6. On-Chip Debug Port for UniPHY-based EMIF IP

13.7. Example Tcl Script for Running the Legacy EMIF Debug Toolkit

13.8. Document Revision History

Visible to Intel only — GUID: bos1493517947427

Ixiasoft

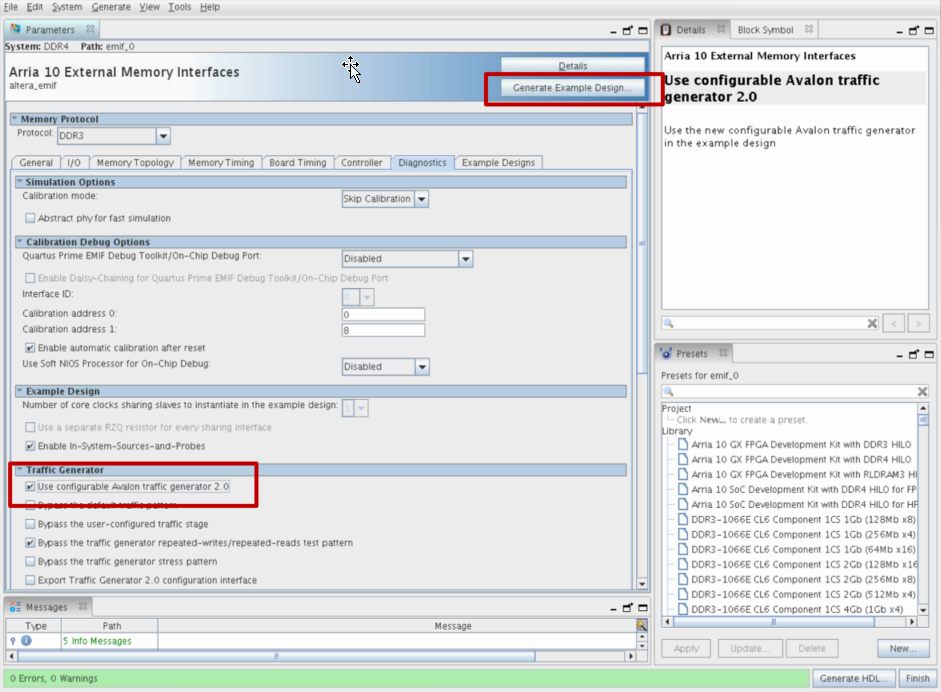

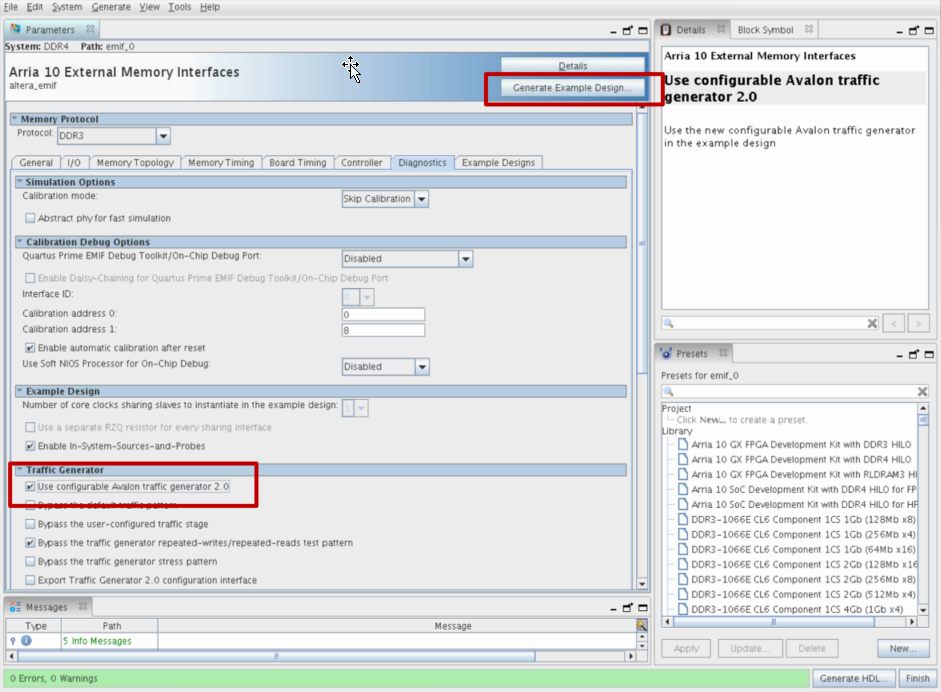

16.10.1. Configuring the Traffic Generator 2.0

The traffic generator replaces user logic to generate traffic to the external memory. You must incorporate the traffic generator design into the EMIF IP design during IP generation.

When you generate the example design in the parameter editor, the traffic generator module and EMIF IP are generated together. If you have an example design with the Traffic Generator 2.0 enabled, you can configure the traffic pattern using the EMIF Debug Toolkit.

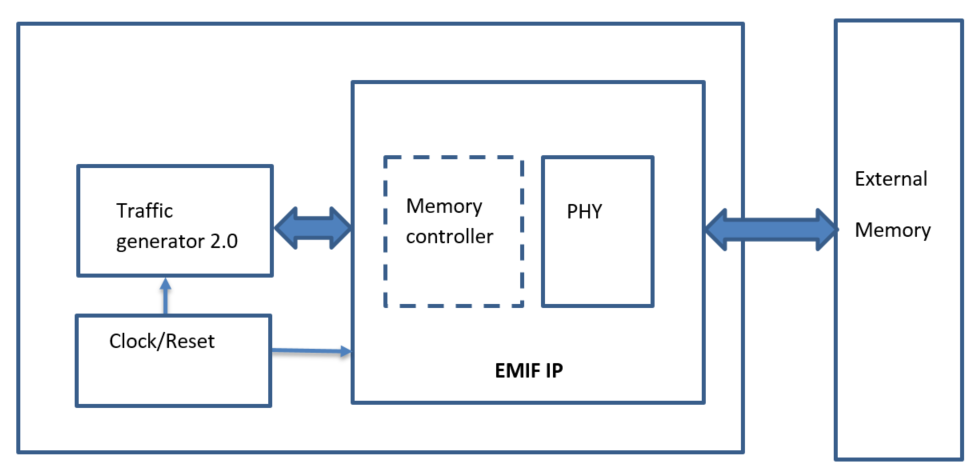

Figure 214. Traffic Generator 2.0 Generated with EMIF IP in Example Design Mode

Generating the External Memory Interface

- Select the FPGA and Memory parameters.

- On the Diagnostics tab, configure the following parameters:

- Select Use Configurable Avalon Traffic Generator 2.0.

- Configure the desired traffic pattern, by specifying traffic patterns to be bypassed. The traffic pattern not bypassed is issued to the memory immediately after completion of calibration. You can choose to bypass any of the following traffic patterns:

- Bypass the default traffic pattern Specifies not to use the default traffic patterns from the traffic generator. The default patterns include single read/write, byte-enabled read/write, and block read/write.

- Bypass the user-configured traffic stage. Specifies to skip the stage that uses the user-defined test bench file to configure the traffic generator in simulation.

- Bypass the traffic generator repeated-writes/repeated-reads test pattern. Bypasses the traffic generator's repeat test stage, which causes every write and read to be repeated several times.

- Bypass the traffic generator stress pattern. Bypasses a test stage intended to stress-test signal integrity and memory interface calibration.

- Export Traffic Generator 2.0 configuration interface. Instantiates a port for traffic generator configuration. Use this port if the traffic generator is to be configured by user logic.

- Click Generate Example Design to generate the EMIF IP, including the Traffic Generator 2.0 design, with the traffic pattern that you have configured.

Note: If you click the Generate HDL option instead, the Traffic Generator 2.0 design is not included in the generated IP.

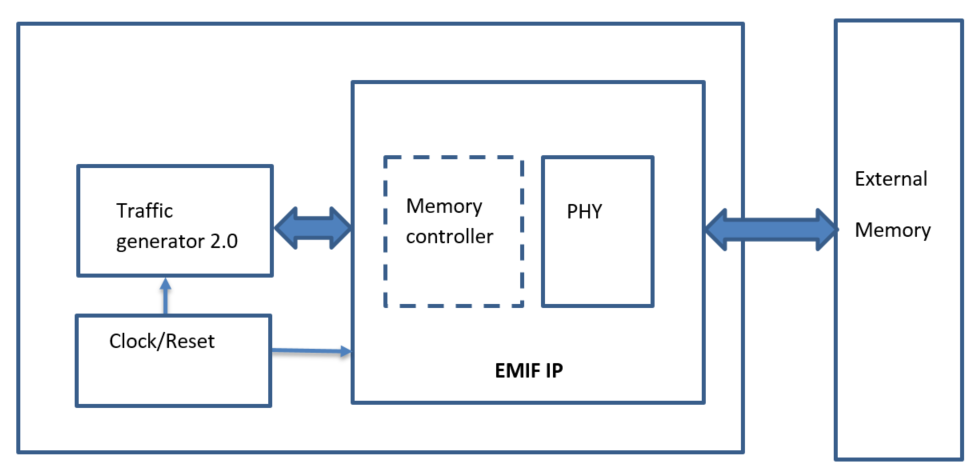

Figure 215. Enabling the Traffic Generator 2.0 in the Parameter Editor