Visible to Intel only — GUID: wqg1631006665072

Ixiasoft

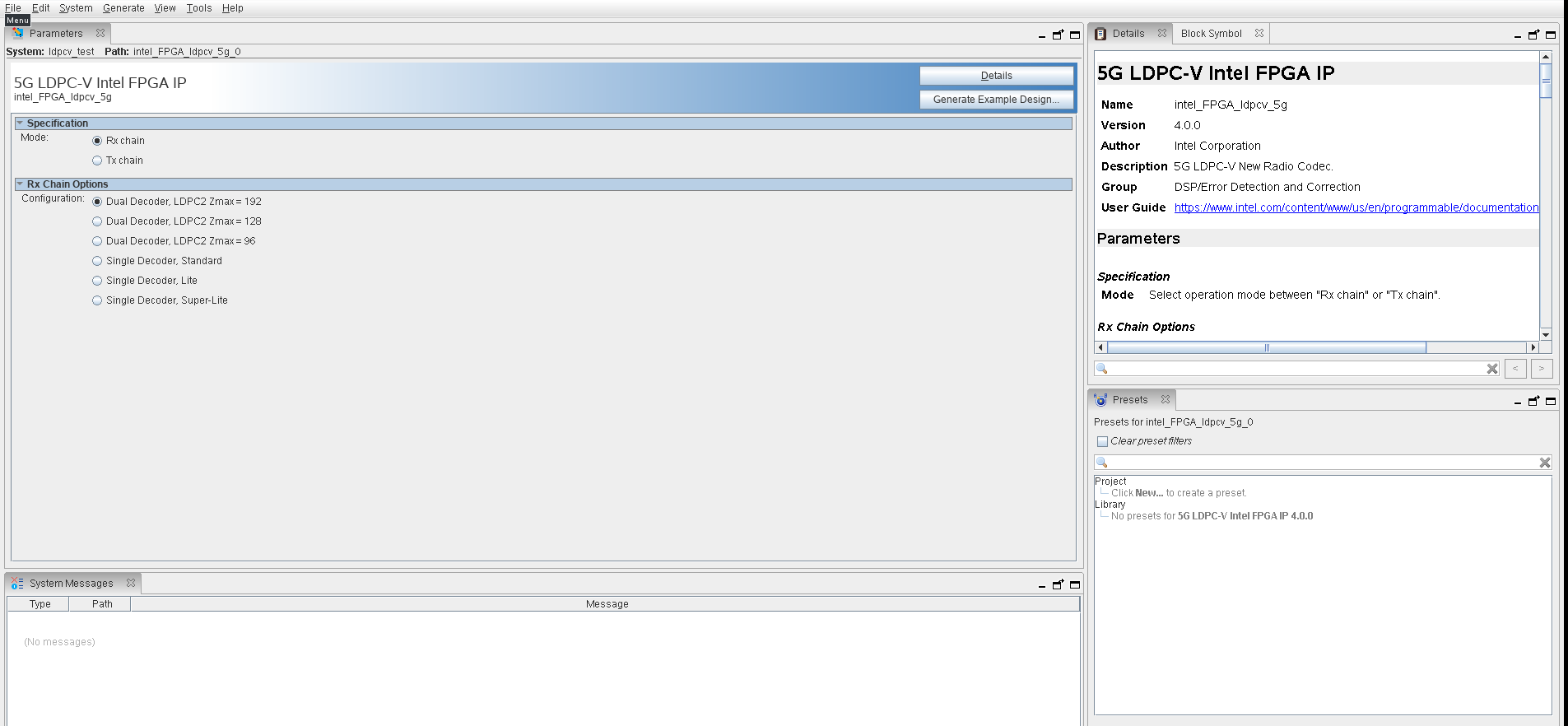

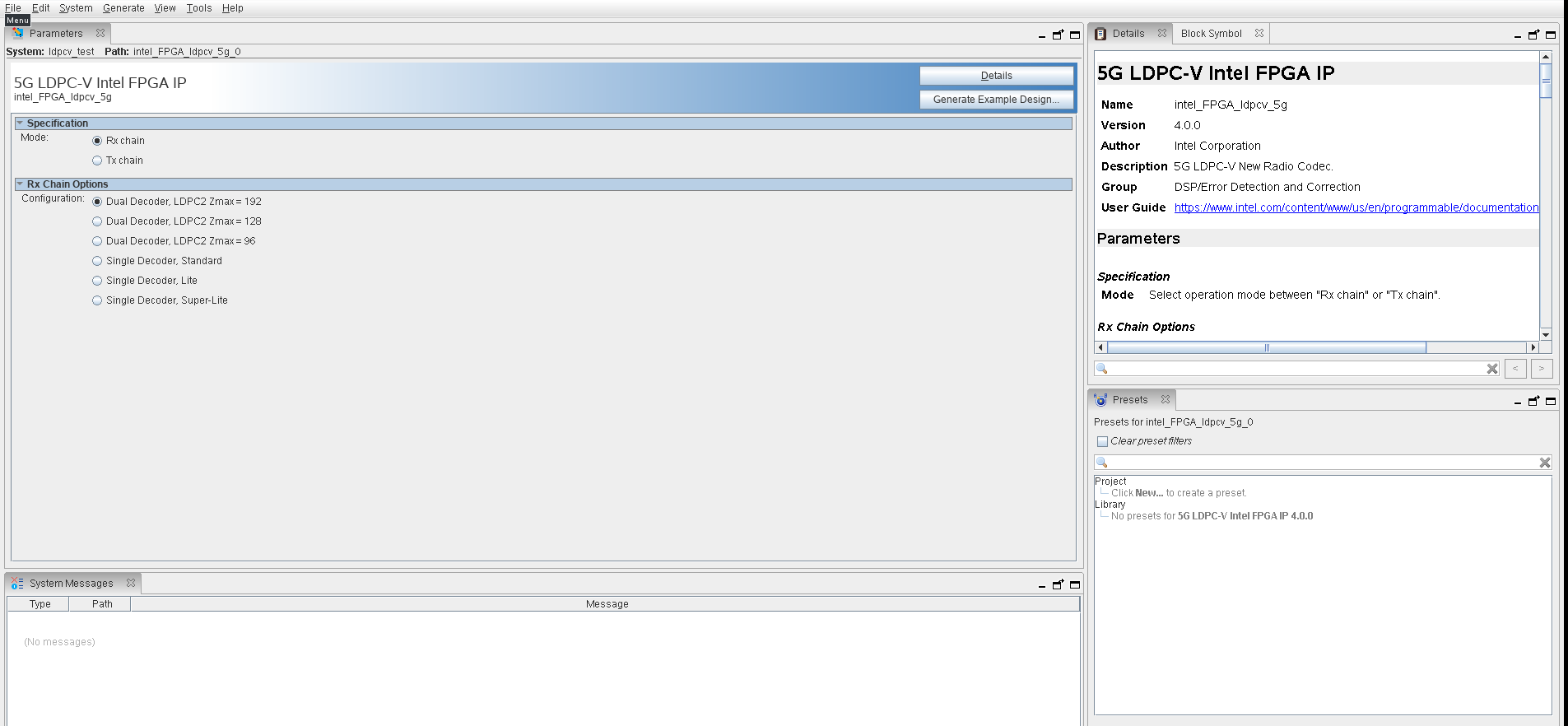

3.2.1. 5G LDPC-V IP Parameters

| Parameter Name | Blocks | Description |

|---|---|---|

| Configuration. | ||

| Dual Decoder, LDPC2 Zmax = 192 |

|

LDPC1 is a standard LDPC engine that processes all codewords. LDPC2 can increase throughput by processing smaller codewords up to Zmax= 192. |

| Dual Decoder, LDPC2 Zmax = 128 | LDPC1 is a standard LDPC engine that processes all codewords. LDPC2 can increase throughput by processing smaller codewords up to Zmax = 128. | |

| Dual Decoder, LDPC2 Zmax = 96 | LDPC1 is a standard LDPC engine that processes all codewords. LDPC2 can increase throughput by processing smaller codewords up to Zmax = 96. | |

| Single Decoder, Standard |

|

Standard design. |

| Single Decoder, Lite | This design achieve lower power. | |

| Single Decoder, Super-Lite | This design is configured to achieve lowest power. | |

Figure 6. 5G LDPC Parameter Editor