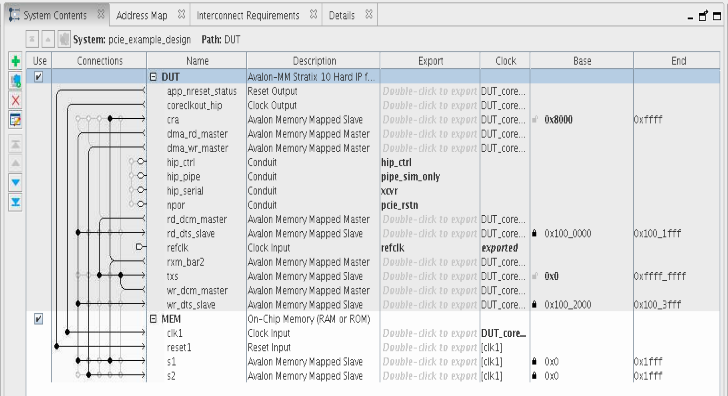

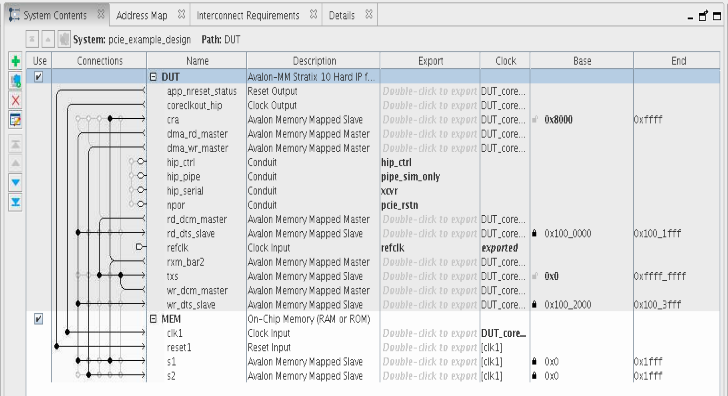

2.1. Functional Description for the DMA Design Example

The DMA design example simulation testbench includes the following components:

- DUT: The Intel® Stratix® 10 Hard IP for PCI Express Endpoint with the Enable Avalon® -MM DMA parameter and the Enable non-bursting Avalon® -MM slave interface with individual byte access (TXS) parameter turned on.

Note: If the parameter Instantiate internal descriptor controller is set to Enabled , then there will be no PCIE_DMA_CONTROLLER component instantiated at the system level.

- MEM: An on-chip RAM that connects to the DUT RXM_bar2, an Avalon® -MM master interface.

- A testbench driver that configures the Root Port, Endpoint, writes to Endpoint memory, and programs the descriptor controller.

- A testbench monitor that checks expected results.

Figure 8. DMA Design Example