1.5. Test Results

The following table contains the possible results and their definition.

| Result | Definition |

|---|---|

| PASS | The device under test (DUT) was observed to exhibit conformant behavior. |

| PASS with comments | The DUT was observed to exhibit conformant behavior. However, an additional explanation of the situation is included (example: due to time limitations, only a portion of the testing was performed). |

| FAIL | The DUT was observed to exhibit non-conformant behavior. |

| Warning | The DUT was observed to exhibit behavior that is not recommended. |

| Refer to comments | From the observations, a valid pass or fail could not be determined. An additional explanation of the situation is included. |

The following table shows the results for test cases CGS.1, CGS.2, ILA.1, ILA.2, ILA.3, TL.1, TL.2, SCR.1, and SCR.2 with different values of L, M, F, K, data rate, sampling clock, link clock, and SYSREF frequencies.

| Test No. | L | M | F | SCR | K | Data Rate (Gbps) | ADC Sampling Clock (MHz) | Link Clock (MHz) | Result |

|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 2 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 2 | 1 | 1 | 2 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 3 | 1 | 1 | 2 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 4 | 1 | 1 | 2 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 5 | 1 | 1 | 4 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 6 | 1 | 1 | 4 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 7 | 1 | 1 | 4 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 8 | 1 | 1 | 4 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 9 | 2 | 1 | 1 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 10 | 2 | 1 | 1 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 11 | 2 | 1 | 1 | 0 | 20 | 16.0 | 1600 | 400 | PASS |

| 12 | 2 | 1 | 1 | 1 | 20 | 16.0 | 1600 | 400 | PASS |

| 13 | 2 | 1 | 2 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 14 | 2 | 1 | 2 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 15 | 2 | 1 | 2 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 16 | 2 | 1 | 2 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

| 17 | 4 | 1 | 1 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 18 | 4 | 1 | 1 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 19 | 4 | 1 | 1 | 0 | 20 | 15.0 | 3000 | 375 | PASS |

| 20 | 4 | 1 | 1 | 1 | 20 | 15.0 | 3000 | 375 | PASS |

| 21 | 4 | 1 | 2 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 22 | 4 | 1 | 2 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 23 | 4 | 1 | 2 | 0 | 16 | 15.0 | 3000 | 375 | PASS |

| 24 | 4 | 1 | 2 | 1 | 16 | 15.0 | 3000 | 375 | PASS |

| 25 | 8 | 1 | 1 | 0 | 32 | 7.5 | 3000 | 187.5 | PASS |

| 26 | 8 | 1 | 1 | 1 | 32 | 7.5 | 3000 | 187.5 | PASS |

| 27 | 8 | 1 | 1 | 0 | 20 | 7.5 | 3000 | 187.5 | PASS |

| 28 | 8 | 1 | 1 | 1 | 20 | 7.5 | 3000 | 187.5 | PASS |

| 29 | 8 | 1 | 2 | 0 | 32 | 7.5 | 3000 | 187.5 | PASS |

| 30 | 8 | 1 | 2 | 1 | 32 | 7.5 | 3000 | 187.5 | PASS |

| 31 | 8 | 1 | 2 | 0 | 16 | 7.5 | 3000 | 187.5 | PASS |

| 32 | 8 | 1 | 2 | 1 | 16 | 7.5 | 3000 | 187.5 | PASS |

| 33 | 1 | 2 | 4 | 0 | 32 | 16.0 | 400 | 400 | PASS |

| 34 | 1 | 2 | 4 | 1 | 32 | 16.0 | 400 | 400 | PASS |

| 35 | 1 | 2 | 4 | 0 | 16 | 16.0 | 400 | 400 | PASS |

| 36 | 1 | 2 | 4 | 1 | 16 | 16.0 | 400 | 400 | PASS |

| 37 | 1 | 2 | 8 | 0 | 32 | 16.0 | 400 | 400 | PASS |

| 38 | 1 | 2 | 8 | 1 | 32 | 16.0 | 400 | 400 | PASS |

| 39 | 1 | 2 | 8 | 0 | 16 | 16.0 | 400 | 400 | PASS |

| 40 | 1 | 2 | 8 | 1 | 16 | 16.0 | 400 | 400 | PASS |

| 41 | 2 | 2 | 2 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 42 | 2 | 2 | 2 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 43 | 2 | 2 | 2 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 44 | 2 | 2 | 2 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 45 | 2 | 2 | 4 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 46 | 2 | 2 | 4 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 47 | 2 | 2 | 4 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 48 | 2 | 2 | 4 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 49 | 4 | 2 | 1 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 50 | 4 | 2 | 1 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 51 | 4 | 2 | 1 | 0 | 20 | 16.0 | 1600 | 400 | PASS |

| 52 | 4 | 2 | 1 | 1 | 20 | 16.0 | 1600 | 400 | PASS |

| 53 | 4 | 2 | 2 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 54 | 4 | 2 | 2 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 55 | 4 | 2 | 2 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 56 | 4 | 2 | 2 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

| 57 | 8 | 2 | 1 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 58 | 8 | 2 | 1 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 59 | 8 | 2 | 1 | 0 | 20 | 15.0 | 3000 | 375 | PASS |

| 60 | 8 | 2 | 1 | 1 | 20 | 15.0 | 3000 | 375 | PASS |

| 61 | 8 | 2 | 2 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 62 | 8 | 2 | 2 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 63 | 8 | 2 | 2 | 0 | 16 | 15.0 | 3000 | 375 | PASS |

| 64 | 8 | 2 | 2 | 1 | 16 | 15.0 | 3000 | 375 | PASS |

| 65 | 1 | 4 | 8 | 0 | 32 | 16.0 | 400 | 400 | PASS |

| 66 | 1 | 4 | 8 | 1 | 32 | 16.0 | 400 | 400 | PASS |

| 67 | 1 | 4 | 8 | 0 | 16 | 16.0 | 400 | 400 | PASS |

| 68 | 1 | 4 | 8 | 1 | 16 | 16.0 | 400 | 400 | PASS |

| 69 | 2 | 4 | 4 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 70 | 2 | 4 | 4 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 71 | 2 | 4 | 4 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 72 | 2 | 4 | 4 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 73 | 2 | 4 | 8 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 74 | 2 | 4 | 8 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 75 | 2 | 4 | 8 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 76 | 2 | 4 | 8 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 77 | 4 | 4 | 2 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 78 | 4 | 4 | 2 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 79 | 4 | 4 | 2 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 80 | 4 | 4 | 2 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

| 81 | 4 | 4 | 4 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 82 | 4 | 4 | 4 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 83 | 4 | 4 | 4 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 84 | 4 | 4 | 4 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

| 85 | 8 | 4 | 1 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 86 | 8 | 4 | 1 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 87 | 8 | 4 | 1 | 0 | 20 | 15.0 | 3000 | 375 | PASS |

| 88 | 8 | 4 | 1 | 1 | 20 | 15.0 | 3000 | 375 | PASS |

| 89 | 8 | 4 | 2 | 0 | 32 | 15.0 | 3000 | 375 | PASS |

| 90 | 8 | 4 | 2 | 1 | 32 | 15.0 | 3000 | 375 | PASS |

| 91 | 8 | 4 | 2 | 0 | 16 | 15.0 | 3000 | 375 | PASS |

| 92 | 8 | 4 | 2 | 1 | 16 | 15.0 | 3000 | 375 | PASS |

| 93 | 2 | 8 | 8 | 0 | 32 | 16.0 | 400 | 400 | PASS |

| 94 | 2 | 8 | 8 | 1 | 32 | 16.0 | 400 | 400 | PASS |

| 95 | 2 | 8 | 8 | 0 | 16 | 16.0 | 400 | 400 | PASS |

| 96 | 2 | 8 | 8 | 1 | 16 | 16.0 | 400 | 400 | PASS |

| 97 | 4 | 8 | 4 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 98 | 4 | 8 | 4 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 99 | 4 | 8 | 4 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 100 | 4 | 8 | 4 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 101 | 4 | 8 | 8 | 0 | 32 | 16.0 | 800 | 400 | PASS |

| 102 | 4 | 8 | 8 | 1 | 32 | 16.0 | 800 | 400 | PASS |

| 103 | 4 | 8 | 8 | 0 | 16 | 16.0 | 800 | 400 | PASS |

| 104 | 4 | 8 | 8 | 1 | 16 | 16.0 | 800 | 400 | PASS |

| 105 | 8 | 8 | 2 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 106 | 8 | 8 | 2 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 107 | 8 | 8 | 2 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 108 | 8 | 8 | 2 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

| 109 | 8 | 8 | 4 | 0 | 32 | 16.0 | 1600 | 400 | PASS |

| 110 | 8 | 8 | 4 | 1 | 32 | 16.0 | 1600 | 400 | PASS |

| 111 | 8 | 8 | 4 | 0 | 16 | 16.0 | 1600 | 400 | PASS |

| 112 | 8 | 8 | 4 | 1 | 16 | 16.0 | 1600 | 400 | PASS |

The following table shows the results for test cases DL.1, DL.2, and DL.3 with different values of L, M, F, SCR, K, data rate, sampling clock, link clock, and SYSREF frequencies.

| Test No. | L | M | F | SCR | K | Data Rate (Gbps) |

Sampling Clock (MHz) |

Link Clock (MHz) |

Result | Latency (Link Clock Cycles) |

|---|---|---|---|---|---|---|---|---|---|---|

| DL.1 | 1 | 1 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 1 | 1 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 1 | 1 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 1 | 1 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 1 | 1 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 1 | 1 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 2 | 1 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | 60(K=20) 76(K=32) |

| DL.2 | 2 | 1 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 2 | 1 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 2 | 1 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 76(K=16) 115(K=32) |

| DL.2 | 2 | 1 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 2 | 1 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 4 | 1 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | 58(K=20) 75(K=32) |

| DL.2 | 4 | 1 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 4 | 1 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 4 | 1 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 4 | 1 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 4 | 1 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 8 | 1 | 1 | 1 | 20/32 | 7.5 | 3000 | 187.5 | PASS | 56(K=20, SCR=1) 58(K=20, SCR=0) 70(K=32) |

| DL.2 | 8 | 1 | 1 | 1 | 20/32 | 7.5 | 3000 | 187.5 | PASS | |

| DL.3 | 8 | 1 | 1 | 1 | 20/32 | 7.5 | 3000 | 187.5 | PASS | |

| DL.1 | 8 | 1 | 2 | 1 | 16/32 | 7.5 | 3000 | 187.5 | PASS | 70(K=16) 102(K=32) |

| DL.2 | 8 | 1 | 2 | 1 | 16/32 | 7.5 | 3000 | 187.5 | PASS | |

| DL.3 | 8 | 1 | 2 | 1 | 16/32 | 7.5 | 3000 | 187.5 | PASS | |

| DL.1 | 1 | 2 | 4 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 1 | 2 | 4 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.3 | 1 | 2 | 4 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.1 | 1 | 2 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | 195(K=16) 323(K=32) |

| DL.2 | 1 | 2 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.3 | 1 | 2 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.1 | 2 | 2 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 2 | 2 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 2 | 2 | 2 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 2 | 2 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 2 | 2 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 2 | 2 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 4 | 2 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | 59(K=20) 75(K=32) |

| DL.2 | 4 | 2 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 4 | 2 | 1 | 1 | 20/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 4 | 2 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 4 | 2 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 4 | 2 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 8 | 2 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | 58(K=20) 75(K=32) |

| DL.2 | 8 | 2 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 8 | 2 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 8 | 2 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 8 | 2 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 8 | 2 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 1 | 4 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | 196(K=16) 324(K=32) |

| DL.2 | 1 | 4 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.3 | 1 | 4 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.1 | 2 | 4 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 116(K=16) 195(K=32) |

| DL.2 | 2 | 4 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 2 | 4 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 2 | 4 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 195(K=16) 323(K=32) |

| DL.2 | 2 | 4 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 2 | 4 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 4 | 4 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 4 | 4 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 4 | 4 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 4 | 4 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 4 | 4 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 4 | 4 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 8 | 4 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | 58(K=16) 75(K=32) |

| DL.2 | 8 | 4 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 8 | 4 | 1 | 1 | 20/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 8 | 4 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 8 | 4 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.3 | 8 | 4 | 2 | 1 | 16/32 | 15.0 | 3000 | 375 | PASS | |

| DL.1 | 2 | 8 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | 196(K=16) 323(K=32) |

| DL.2 | 2 | 8 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.3 | 2 | 8 | 8 | 1 | 16/32 | 16.0 | 400 | 400 | PASS | |

| DL.1 | 4 | 8 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 4 | 8 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 4 | 8 | 4 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 4 | 8 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | 195(K=16) 323(K=32) |

| DL.2 | 4 | 8 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.3 | 4 | 8 | 8 | 1 | 16/32 | 16.0 | 800 | 400 | PASS | |

| DL.1 | 8 | 8 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 75(K=16) 115(K=32) |

| DL.2 | 8 | 8 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 8 | 8 | 2 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.1 | 8 | 8 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | 115(K=16) 195(K=32) |

| DL.2 | 8 | 8 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS | |

| DL.3 | 8 | 8 | 4 | 1 | 16/32 | 16.0 | 1600 | 400 | PASS |

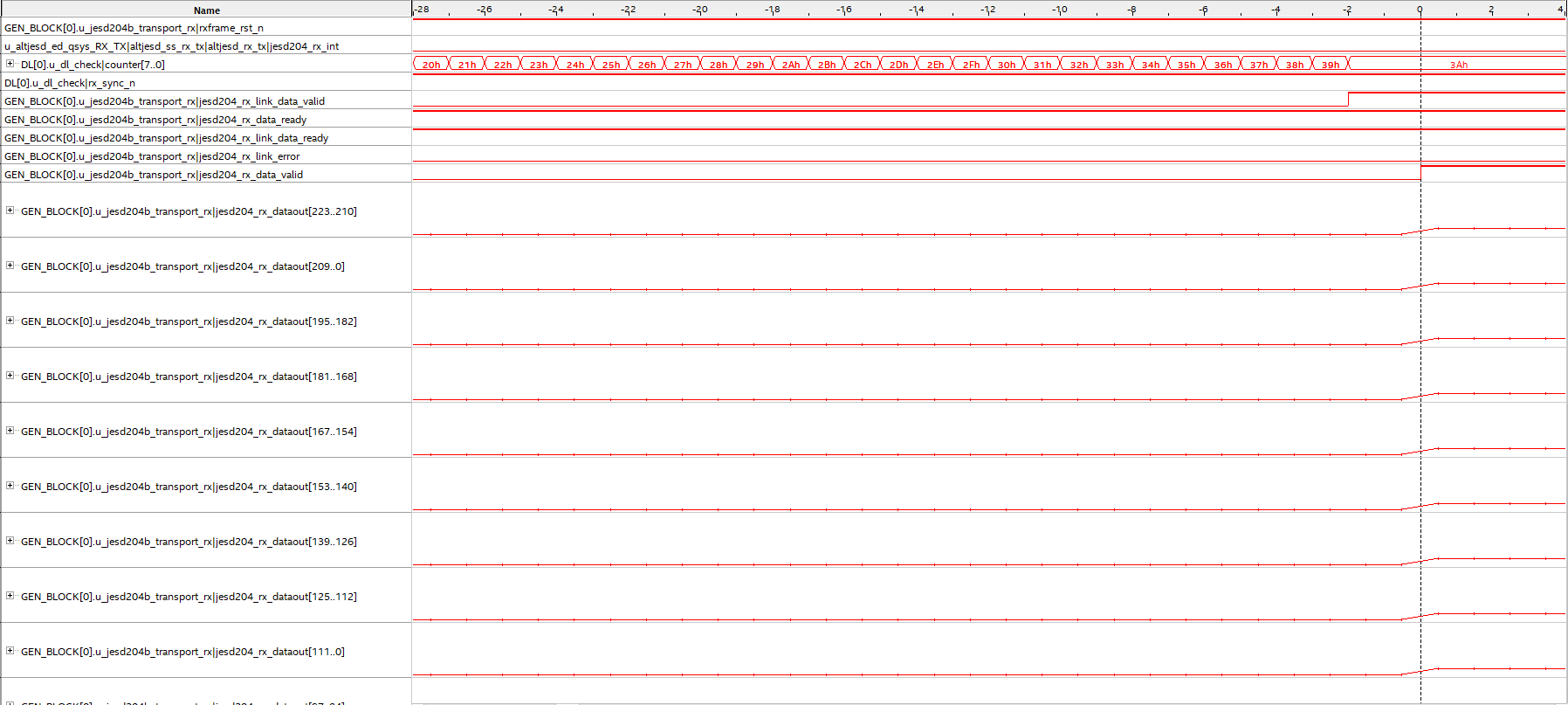

The following figure shows the Signal Tap waveform of the link latency count from the deassertion of SYNC~ to the assertion of the jesd204_rx_link_valid signal. The link latency count (in link clock cycles) measures the first user data output latency.