Visible to Intel only — GUID: kyv1634151468002

Ixiasoft

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

Visible to Intel only — GUID: kyv1634151468002

Ixiasoft

BAS support is enabled on the hardware. Enable the following flag in user/common/include/ifc_libmqdma.h

#define PCIe_SLOT 0 /* 0 – x16, 1 – x8, 2 - x4 */

To enable BAS in common.mk (software/user/common/mk/common.mk), use the following command:

__cflags += -DIFC_MCDMA_BAS_EN

Commands:

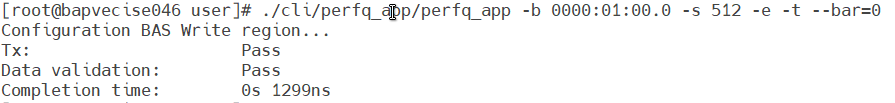

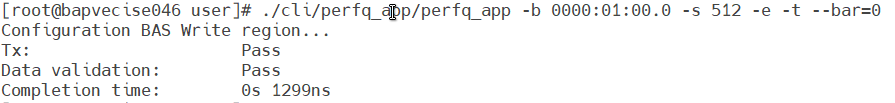

To verify the write operation:

./cli/perfq_app/perfq_app -b 0000:01:00.0 -s 512 -e -t --bar=0

Figure 33. BAS Write Operation

To verify the read operation:

./cli/perfq_app/perfq_app -b 0000:01:00.0 -s 512 -e -r --bar=0

Figure 34. BAS Read Operation

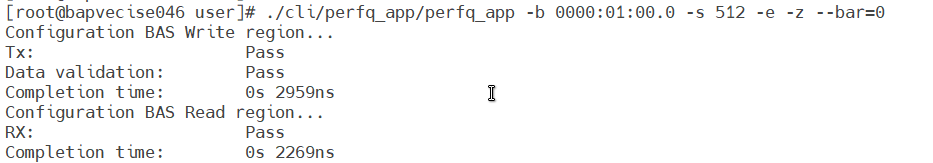

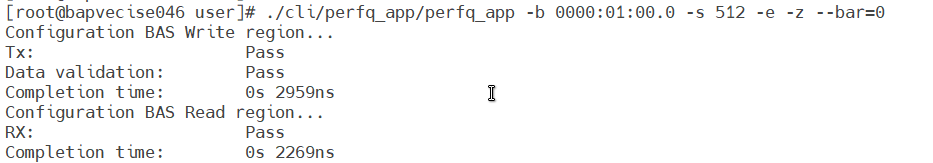

To verify the write and read operation:

./cli/perfq_app/perfq_app -b 0000:01:00.0 -s 512 -e -z --bar=0

Figure 35. BAS Write and Read Operation

Performance test:

The below log is collected on Gen3x16 P-Tile:

./cli/perfq_app/perfq_app -b 0000:01:00.0 -s 16384 –-bas_perf -z --bar=0

Figure 36. BAS Write and Read Performance Test

Note: You may not able to proceed with -z option. Please add flag #define IFC_QDMA_INTF_AVST in user/common/include/mcdma_ip_params.h as a workaround to make it work.

Note: In case of VFIO, to run BAM+BAS+MCDMA, you need to create at least 3 VFs and run on each VFs respectively. If you try to use one VF to run BAM+BAS+MCDMA simultaneously in case of VFIO, it prompts with a resource busy.