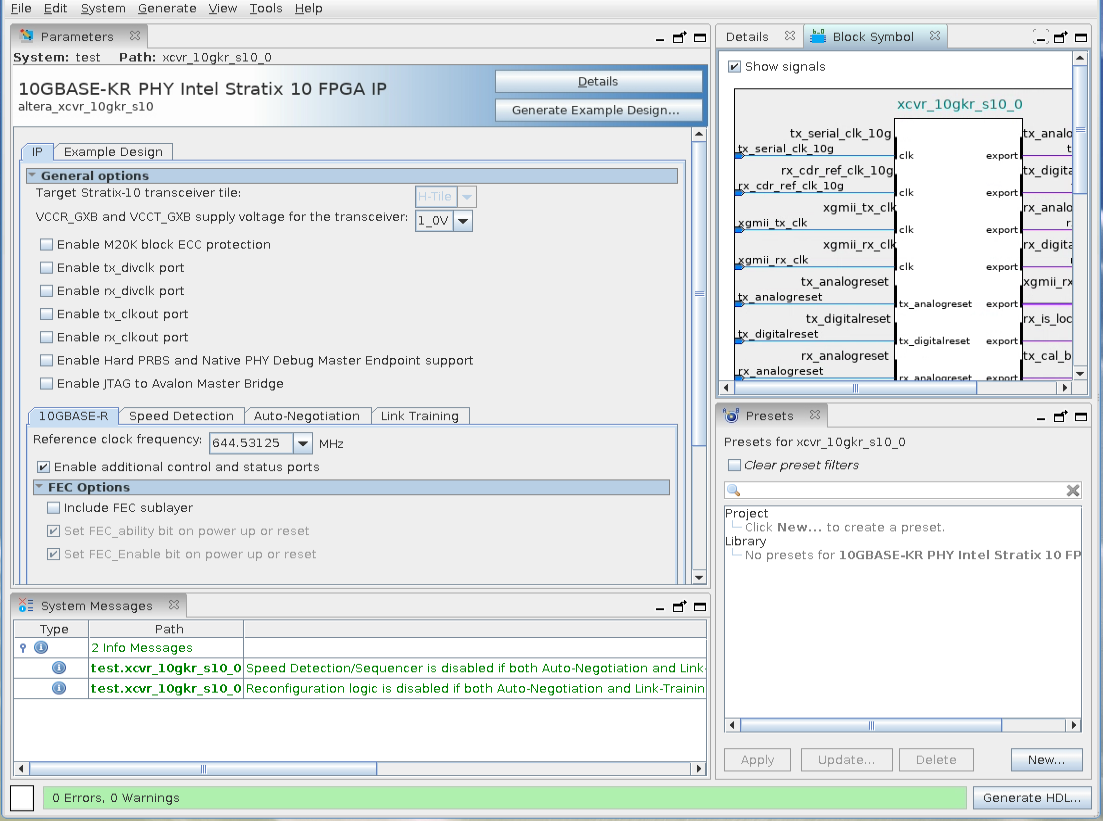

3. Parameter Settings

The Intel® Stratix® 10 10GBASE-KR PHY parameter editor has an IP tab and an Example Design tab. For information about the Example Design, refer to the Design Example section.

| Parameter | Options | Description |

|---|---|---|

| General Options | ||

| Target Stratix-10 transceiver tile | L-Tile, H-Tile | Specifies the transceiver tile on your target Intel® Stratix® 10 device. The Device setting of the Intel® Quartus® Prime Pro Edition project in which you generate the IP core determines the transceiver tile type. In the current version of the Intel® Quartus® Prime Pro Edition, this parameter is grayed out. The correct tile is derived when you select a device for the project. The IP generates the correct transceiver tile type for your target Intel® Stratix® 10 device. |

| VCCR_GXB and VCCT_GXB supply voltage for the transceiver | 1_0V, 1_1V | Selects the VCCR_GXB and VCCT_GXB supply voltage for the transceiver. For 10 Gbps data rate, you can select this value either to 1 V or 1.1 V. |

| Enable M20K block ECC protection | On/Off | When you turn on this parameter, you enable error correction code (ECC) support on the embedded Nios® II CPU system. |

| Enable tx_divclk port | On/Off | When you turn on this parameter, the tx_pma_div_clkout port is enabled. Refer to the Clock and Reset Interfaces section for more information about this port. |

| Enable rx_divclk port | On/Off | When you turn on this parameter, the rx_pma_div_clkout port is enabled. Refer to the Clock and Reset Signals section for more information about this port. |

| Enable tx_clkout port | On/Off | When you turn on this parameter, the tx_clkout port is enabled. Refer to the Clock and Reset Signals section for more information about this port. |

| Enable rx_clkout port | On/Off | When you turn on this parameter, the rx_clkout port is enabled. Refer to the Clock and Reset Signals section for more information about this port. |

| Enable Hard PRBS support and Native PHY Debug Master Endpoint support | On/Off | When you turn on this parameter, you enable the Native PHY Debug Master Endpoint (NPDME) and Hard PRBS data generation and checking logic in the Native PHY. The transceiver toolkit (TTK) requires NPDME to be enabled in the Native PHY IP core. |

| Enable JTAG to Avalon Master Bridge | On/Off | If turned on, the IP core includes a JTAG to Avalon-MM Master bridge connecting internally to status and reconfiguration registers. This allows to run the Ethernet Link Inspector using the System Console |

| Tab: 10GBASE-R | ||

| Reference clock frequency | 644.53125 MHz 322.265625 MHz |

Specifies the input reference clock frequency. |

| Enable additional control and status ports | On/Off | When you turn on this parameter, the core includes the rx_block_lock and rx_hi_ber output. |

| FEC Options | ||

| Include FEC sublayer | On/Off | When you turn on this parameter, the core includes logic to support hard Clause 74 FEC. |

| Set FEC_ability bit on power up and reset | On/Off | When you turn on this parameter, the core sets the Assert KR FEC Ability bit (0xB0[16]) FEC ability bit during power up and reset, causing the core to assert the FEC ability. This option is required for FEC functionality. This parameter is available if you turn on Include FEC sublayer. |

| Set FEC_Enable bit on power up and reset | On/Off | When you turn on this parameter, the IP core sets the KR FEC Request bit (0xB0[18]) during power up and reset, causing the core to request the FEC ability during auto-negotiation. This option is required for FEC functionality. This parameter is available if you turn on Include FEC sublayer. |

| Tab: Speed Detection | ||

| Avalon-MM clock frequency | 156.25 MHz | Specifies the clock frequency for mgmt_clk. The legal range is 100 MHz to 161 MHz (inclusive). This parameter is available if you turn on either Enable Auto-Negotiation or Enable Link Training |

| Link fail inhibit time for 10Gb Ethernet | 504 ms | Specifies the time before link_status is set to FAIL or OK. A link fails if the link_fail_inhibit_time has expired before link_status is set to OK. The Ethernet standard range is 500 ms to 510 ms and IP core legal range is 10 ms to 1270 ms. For more information, refer to Clause 73 Auto Negotiation for Backplane Ethernet in IEEE Std 802.3-2015. This parameter is available if you turn on either Enable Auto-Negotiation or Enable Link Training |

| Enable PCS-Mode port | On/Off | Enables or disables the PCS-Mode port. |

| Tab: Auto-Negotiation | ||

| Enable Auto-Negotiation | On/Off | When you turn on this parameter, the IP core includes logic to implement auto-negotiation feature. |

| Pause ability-C0 | On/Off | When you turn on this parameter, the IP core indicates on the Ethernet link that it supports symmetric pauses. For more information, refer to IEEE 802.3 Annex 28B. This parameter is available if you turn on Enable Auto-Negotiation. |

| Pause ability-C1 | On/Off | When you turn on this parameter, the IP core indicates on the Ethernet link that it supports asymmetric pauses. For more information, refer to IEEE 802.3 Annex 28B. This parameter is available if you turn on Enable Auto-Negotiation. |

| Tab: Link Training | ||

| Enable Link Training | On/Off | Enables or disables the Link Training feature. |

| Maximum bit error count | 15, 31, 63, 127, 255, 511, 1023 | Specifies the number of bit errors for the error counter expected during each step of the link training. The number of errors depends upon the amount of time for each step and the quality of the physical link media. The default value is 511. This parameter is available if you turn on Enable Link Training. |

| Number of frames to send before sending actual data | 127, 255 | Specifies the number of additional training frames the local link partner delivers to ensure that the link partner can correctly detect the local receiver state. This number is the value of wait_timer. The default value is 127. This parameter is available if you turn on Enable Link Training. |

| PMA parameters (only available when you turn on Enable Link Training) |

||

| VMAXRULE | 0-31 | Specifies the maximum VOD. The default value is 30. |

| VMINRULE | 0-31 | Specifies the minimum VOD. The default value is 6. |

| VODMINRULE | 0-31 | Specifies the minimum VOD for the first tap. The default value is 14. |

| VPOSTRULE | 0-38 | Specifies the maximum value that the internal algorithm for pre-emphasis will ever test in determining the optimum post-tap setting. The default value is 25. |

| VPRERULE | 0-31 | Specifies the maximum value that the internal algorithm for pre-emphasis will ever test in determining the optimum pre-tap setting. The default value is 16. |

| PREMAINVAL | 0-31 | Specifies the Preset VOD value. This value is set by the Preset command of the link training protocol, defined in Clause 72.6.10.2.3.1 of the Link Training protocol. This is the value from which the algorithm starts. The default value is 30. |

| PREPOSTVAL | 0-31 | Specifies the preset Post-tap value. The default value is 0. |

| PREPREVAL | 0-15 | Specifies the preset Pre-tap value. The default value is 0. |

| INITMAINVAL | 0-31 | Specifies the initial VOD value. This value is set by the Initialize command of the link training protocol. The default value is 25. |

| INITPOSTVAL | 0-38 | Specifies the initial Post-tap value. The default value is 13. |

| INITPREVAL | 0-15 | Specifies the initial Pre-tap value. The default value is 3. |