Visible to Intel only — GUID: mhi1440429084444

Ixiasoft

Visible to Intel only — GUID: mhi1440429084444

Ixiasoft

1. Introduction to Quartus® Prime Pro Edition

This user guide describes basic concepts, files, and design flow of the Quartus® Prime Pro Edition software, including initial design planning considerations, selecting a starting point to set up your Quartus® Prime Pro Edition project and managing those projects and working with intellectual property (IP).

The Quartus® Prime design suite is a comprehensive development platform to design with Intel FPGAs1, from design entry and synthesis to optimization, verification, simulation, and binary generation. The Quartus® Prime software supports fast design processing, straightforward device programming, and integration with other industry-standard EDA tools. The user interface makes it easy for you to focus on your design—not on the design tool. The modular compiler streamlines the FPGA development process and ensures the highest performance for the least effort.

Quartus® Prime Pro Edition Software Quick Start Steps

Use the following links to get started with the Quartus® Prime Pro Edition software:

| Step | Useful Links | |

|---|---|---|

| Determine the System Requirements | Verify hardware and software requirements and review Quartus® Prime Pro Edition software release notes. | |

| Download the software | Download the latest Quartus® Prime Pro Edition software. | |

| Install the software | Install the latest Quartus® Prime Pro Edition software. | |

| Generate 90-days Fixed-node License | Generate 90- days free license in Intel® FPGA Self-Service Licensing Center (SSLC). | |

| Start the software | On Windows: Use one of the following options:

On Linux:

|

Starting the Quartus® Prime Software |

| Set up the generated license in the Quartus® Prime Pro Edition software | In the Quartus® Prime Pro Edition software, click Tools > License Setup, browse and select the license file, and click OK. | |

| Quartus® Prime Software Home Page | Main page of the Quartus® Prime software. |

|

| Plan FPGA Design for RTL Flow | Planning for RTL flow is an essential step for advanced FPGA design. Determining your design priorities early on helps you to choose the best device, tools, features, and methodologies for your design. | Plan FPGA Design for RTL Flow |

| Create your FPGA project | The Quartus® Prime software makes it easy for you to quickly setup a new FPGA design project. | Creating a New FPGA Design Project |

Quartus® Prime Software Editions

The Quartus® Prime Software is available in three editions based on your design requirements:

| Pro Edition | Standard Edition | Lite Edition | |

|---|---|---|---|

|

Optimized to support the advanced features in Intel FPGAs and SoCs with the following device families:

|

Includes extensive support for earlier device families in addition to the following device families:

|

An ideal entry point to Intel’s high-volume device families and is available as a free download with no license file required. |

Supported Features

The following is the Quartus® Prime feature support matrix:

The following features are only available in the Quartus® Prime Pro Edition software:

| Feature | Description |

|---|---|

| Hyper-Aware Design Flow | Use Hyper-Retiming to reach the highest performance in Agilex™ 5, Agilex™ 7, and Stratix® 10 devices. |

| Advanced synthesis | Integrates new, stricter language parser supporting all major IEEE RTL languages, with enhanced algorithms, and parallel synthesis capabilities, and support for SystemVerilog 2009. |

| Hierarchical project structure | Preserves individual post-synthesis, post-placement, and post-place and route results for design instances. Optimizes without impacting other partition placement or routing. |

| Incremental Fitter Optimizations | Run and optimize Fitter stages incrementally. Each Fitter stage generates detailed reports. |

| Faster, more accurate I/O placement | Plan interface I/O in Interface Planner. |

| Platform Designer (Pro) | Builds on the system design and custom IP integration capabilities of Platform Designer (Standard). Platform Designer (Pro) introduces hierarchical isolation between system interconnect and IP components. |

| Block-Based Design Flows | Preserve and reuse design blocks at various stages of compilation. |

Quartus® Prime Pro Edition software does not support the following Quartus® Prime Standard Edition features:

- I/O Timing Analysis

- NativeLink third party tool integration (other third-party tool integration available)

- Video and Image Processing Suite IP Cores

- Talkback features

- Various register merging and duplication settings

- Saving a node-level netlist as .vqm or RTL to schematic conversion

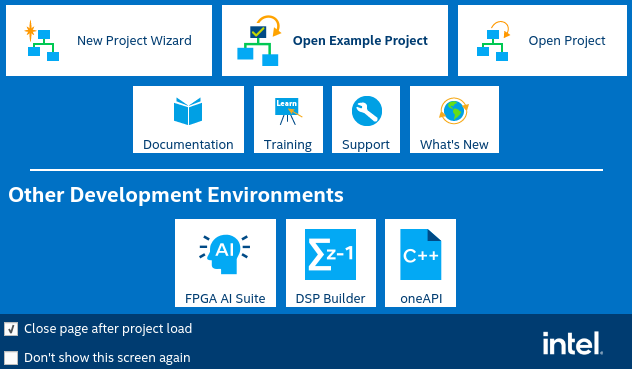

Supported Intel FPGA Developmental Tools

The Quartus® Prime software suite supports the following Intel FPGA development tools:

| Tools | Description |

|---|---|

| Questa*-Intel® FPGA Edition | Simulates FPGA designs using Intel® -specific simulation libraries. It includes all features of Siemens EDA Questa* Core, including behavioral simulation, HDL test benches, and Tcl scripting. |

| Intel® Advanced Link Analyzer | Analyzes jitter/noise and evaluates high-speed serial link performance. It is an ideal predesign tool supporting Intel FPGA IBIS-AMI standards and enhanced models to help you understand how Intel® FPGA solutions can fit your system requirements. |

| Intel® SoC FPGA Embedded Development Suite | A comprehensive tool suite for embedded software development on Intel® SoC FPGAs. |

| Ashling* RiscFree* IDE for Intel® FPGAs | Integrated development environment for creating embedded applications on the RISC-V-based Nios® V soft processors and the Arm*-based hard processor system. |

| Intel® HLS Compiler | A high-level synthesis (HLS) tool that accepts untimed C++ code as an input and generates production-quality register transfer level (RTL) code optimized for Intel® FPGAs. This tool accelerates verification time over RTL by raising the abstraction level for FPGA hardware design. Models developed in C++ have typically verified orders of magnitude faster than RTL. |

| DSP Builder for Intel® FPGAs | Supports a model-based design flow from algorithms to hardware in a common environment. |

| Intel® oneAPI Base Toolkit | Enables you to target FPGAs for heterogeneous acceleration and simulate entire system flows by abstracting some parts of the hardware. |

| Intel® Simics® simulator for Intel® FPGAs | A full-system simulator that supports defining, developing, and deploying virtual platforms. |

| FPGA AI Suite | Provides several components to help in enabling Artificial Intelligence (AI) and creating optimized Intel FPGA AI platforms efficiently. |

| Intel® FPGA Power and Thermal Calculator | Estimates your design's power consumption and provides thermal design parameters for Intel FPGA devices, such as Agilex™ 5, Agilex™ 7, and Stratix® 10. |