Visible to Intel only — GUID: mwh1409958328796

Ixiasoft

2.1. Viewing Basic Project Information

2.2. Intel® Quartus® Prime Project Contents

2.3. Managing Project Settings

2.4. Managing Logic Design Files

2.5. Managing Timing Constraints

2.6. Integrating Other EDA Tools

2.7. Exporting Compilation Results

2.8. Migrating Projects Across Operating Systems

2.9. Archiving Projects

2.10. Command-Line Interface

2.11. Managing Projects Revision History

2.7.1. Exporting a Version-Compatible Compilation Database

2.7.2. Importing a Version-Compatible Compilation Database

2.7.3. Creating a Design Partition

2.7.4. Exporting a Design Partition

2.7.5. Reusing a Design Partition

2.7.6. Viewing Quartus Database File Information

2.7.7. Clearing Compilation Results

3.1. Design Planning

3.2. Create a Design Specification and Test Plan

3.3. Plan for the Target Device

3.4. Plan for Intellectual Property Cores

3.5. Plan for Standard Interfaces

3.6. Plan for Device Programming

3.7. Plan for Device Power Consumption

3.8. Plan for Interface I/O Pins

3.9. Plan for other EDA Tools

3.10. Plan for On-Chip Debugging Tools

3.11. Plan HDL Coding Styles

3.12. Plan for Hierarchical and Team-Based Designs

3.13. Design Planning Revision History

4.1. IP Catalog and Parameter Editor

4.2. Installing and Licensing Intel® FPGA IP Cores

4.3. IP General Settings

4.4. Adding IP to IP Catalog

4.5. Best Practices for Intel® FPGA IP

4.6. Specifying the IP Core Parameters and Options ( Intel® Quartus® Prime Pro Edition)

4.7. Modifying an IP Variation

4.8. Upgrading IP Cores

4.9. Simulating Intel® FPGA IP Cores

4.10. Simulating Platform Designer Systems

4.11. Synthesizing IP Cores in Other EDA Tools

4.12. Instantiating IP Cores in HDL

4.13. Support for the IEEE 1735 Encryption Standard

4.14. Introduction to Intel FPGA IP Cores Revision History

5.2.1. Modify Entity Name Assignments

5.2.2. Resolve Timing Constraint Entity Names

5.2.3. Verify Generated Node Name Assignments

5.2.4. Replace Logic Lock (Standard) Regions

5.2.5. Modify Signal Tap Logic Analyzer Files

5.2.6. Remove References to .qip Files

5.2.7. Remove Unsupported Feature Assignments

5.4.1. Verify Verilog Compilation Unit

5.4.2. Update Entity Auto-Discovery

5.4.3. Ensure Distinct VHDL Namespace for Each Library

5.4.4. Remove Unsupported Parameter Passing

5.4.5. Remove Unsized Constant from WYSIWYG Instantiation

5.4.6. Remove Non-Standard Pragmas

5.4.7. Declare Objects Before Initial Values

5.4.8. Confine SystemVerilog Features to SystemVerilog Files

5.4.9. Avoid Assignment Mixing in Always Blocks

5.4.10. Avoid Unconnected, Non-Existent Ports

5.4.11. Avoid Illegal Parameter Ranges

5.4.12. Update Verilog HDL and VHDL Type Mapping

Visible to Intel only — GUID: mwh1409958328796

Ixiasoft

2.8.1. Migrating Design Files and Libraries

Consider file naming differences when migrating projects across operating systems.

- Use appropriate case for your platform in file path references.

- Use a character set common to both platforms.

- Do not change the forward‑slash (/) and back‑slash (\) path separators in the .qsf. The Intel® Quartus® Prime software automatically changes all back‑slash (\) path separators to forward‑slashes (/ )in the .qsf.

- Observe the target platform’s file name length limit.

- Use underscore instead of spaces in file and directory names.

- Change library absolute path references to relative paths in the .qsf.

- Ensure that any external project library exists in the new platform’s file system.

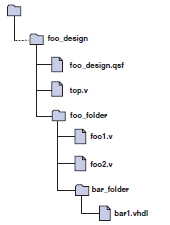

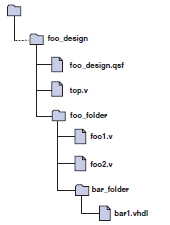

- Specify file and directory paths as relative to the project directory. For example, for a project titled foo_design, specify the source files as: top.v, foo_folder /foo1.v, foo_folder /foo2.v, and foo_folder/bar_folder/bar1.vhdl.

- Ensure that all the subdirectories are in the same hierarchical structure and relative path as in the original platform.

Figure 31. All Inclusive Project Directory Structure