Visible to Intel only — GUID: yte1667519404662

Ixiasoft

1. Answers to Top FAQs

2. Overview of the Intel® FPGA Power and Thermal Calculator

3. Estimating Power Consumption with the Intel® FPGA Power and Thermal Calculator

4. Intel® FPGA Power and Thermal Calculator Graphical User Interface

5. Intel® FPGA Power and Thermal Calculator Pages

6. Factors Affecting the Accuracy of the Intel® FPGA PTC

7. Intel® FPGA Power and Thermal Calculator User Guide Archive

8. Document Revision History for the Intel® FPGA Power and Thermal Calculator User Guide

A. Measuring Static Power

5.1. Intel® FPGA PTC - Power Summary/Navigation

5.2. Intel® FPGA PTC - Common Page Elements

5.3. Intel® FPGA PTC - Main Page

5.4. Intel® FPGA PTC - Logic Page

5.5. Intel® FPGA PTC - RAM Page

5.6. Intel® FPGA PTC - DSP Page

5.7. Intel® FPGA PTC - Clock Page

5.8. Intel® FPGA PTC - PLL Page

5.9. Intel® FPGA PTC - I/O Page

5.10. Intel® FPGA PTC - Transceiver Page

5.11. Intel® FPGA PTC - HPS Page

5.12. Intel® FPGA PTC - Crypto Page

5.13. Intel FPGA PTC - NOC Page

5.14. Intel® FPGA PTC - HBM Page

5.15. Intel® FPGA PTC - Thermal Page

5.16. Intel® FPGA PTC - Report Page

Visible to Intel only — GUID: yte1667519404662

Ixiasoft

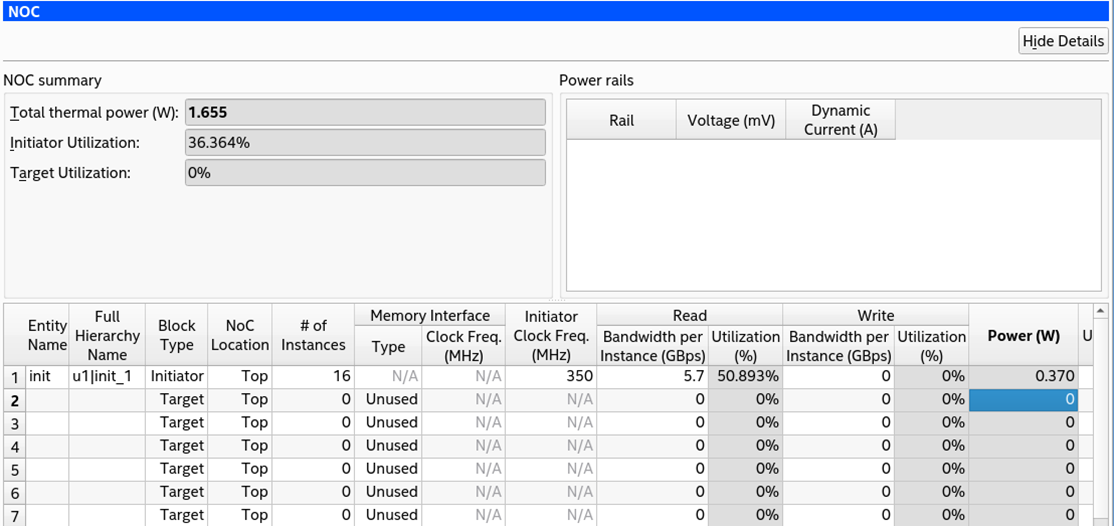

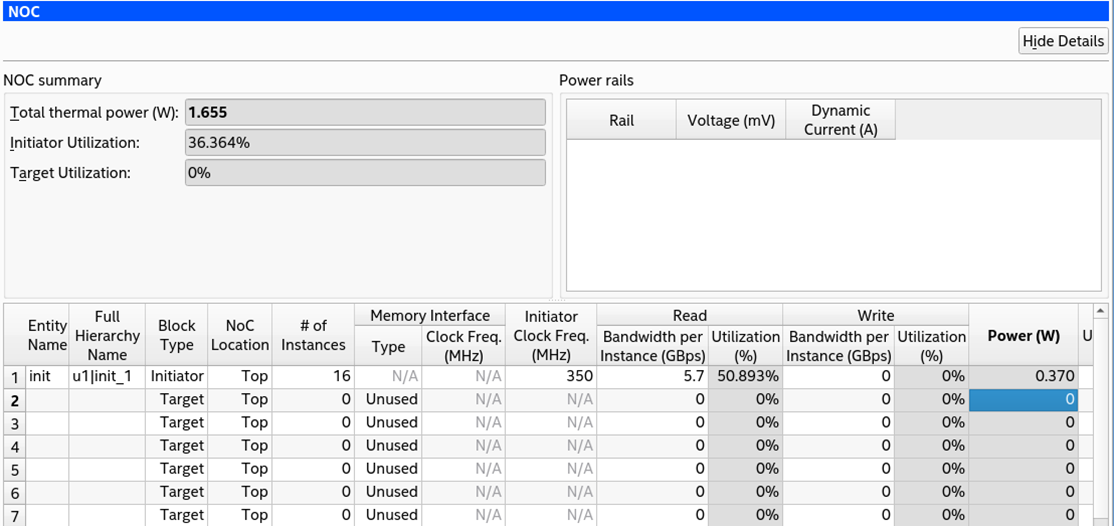

5.13. Intel FPGA PTC - NOC Page

The NOC page of the Intel® FPGA Power and Thermal Calculator (PTC) shows the power information relating to the network-on-chip IP.

To enable parameter entry into the NOC page, first select a device that supports NOC on the Main page or in Device Selection.

Note: Not all Intel® Agilex™ 7 devices have the NOC IP. Parameter entry is unavailable if the currently selected device does not have the NOC IP.

Figure 40. NOC Page of the Intel® FPGA PTC

| Column Heading | Description | |

|---|---|---|

| Entity Name | Specify a name for each entity of the design. This is an optional entry. | |

| Full Hierarchy Name | Specify the hierarchical path relevant to this entry. This is an optional entry. When entering levels of hierarchy, the pipe character (|) denotes a level of hierarchy. | |

| Block Type | Specify whether the block is of type Target or Initiator. | |

| NoC Location | Specify whether the block is located at the Top or Bottom of the device. | |

| # of Instances | Specify the number of instances of this element. A single NoC Initiator Intel FPGA IP may contain multiple initiator interfaces. Similarly, a target memory IP such as the High Bandwidth Memory (HBM2E) Interface FPGA IP may contain multiple target interfaces. This page only reflects the power usage of the NoC targets of IP such as the High Bandwidth Memory (HMB2E) Interface FPGA IP. Estimate the power for the remainder of this IP elsewhere within PTC, for example on the HBM page. | |

| Memory Interface | Type | For target elements only. In the Type column, select between HBM for HBM2e memory or DDR for external memory interfaces implemented in GPIO-B blocks. In the Clock Freq. (MHz) column, enter the clock frequency for these target interfaces |

| Clock Freq. (MHz) | ||

| Initiator Clock Freq. (MHz) | For initiator elements only, enter the clock frequency the user interface for these initiators will operate at. If different initiators operate at different frequencies, they will need to be specified on separate rows. | |

| Read | Bandwidth per Instance (GBps) | For both initiator and target elements. Specify read and write bandwidth in the Bandwidth per Instance (GBps). Initiator or target elements with different bandwidth requirements need to be specified on separate rows. The Utilization (%) displays the bandwidth utilization for each initiator or target. A warning is generated if the read bandwidth utilization and write bandwidth utilization add up to more than 100%. |

| Utilization (%) | ||

| Write | Bandwidth per Instance (GBps) | |

| Utilization (%) | ||

| Power (W) | Reports the power for the total initiators or targets specified on that row. | |

| User Comments | Enter any comments. This is an optional entry. | |

For more information about the NOC, refer to the Intel® Agilex™ 7 M-Series FPGA Network-on-Chip (NoC) User Guide.