Visible to Intel only — GUID: mab1496413141436

Ixiasoft

Visible to Intel only — GUID: mab1496413141436

Ixiasoft

4.9. Reset Behavior

For your HLS component, the reset assertion can be asynchronous but the reset deassertion must be synchronous.

reg [2:0] sync_resetn;

always @(posedge clock or negedge resetn) begin

if (!resetn) begin

sync_resetn <= 3'b0;

end else begin

sync_resetn <= {sync_resetn[1:0], 1'b1};

end

end

wire synchronized_resetn;

assign synchronized_resetn = sync_resetn[2];This synchronizer code is used in the example Intel® Quartus® Prime Pro Edition project that is generated for your components included in an i++ compile. Synchronizers are implemented to minimize synchronization failures due to metastability in asynchronous signal transfers. For more information about metastability, refer to "Managing Metastability with the Intel Quartus Prime Software" in Intel Quartus Prime Pro Edition User Guide: Design Recommendations .

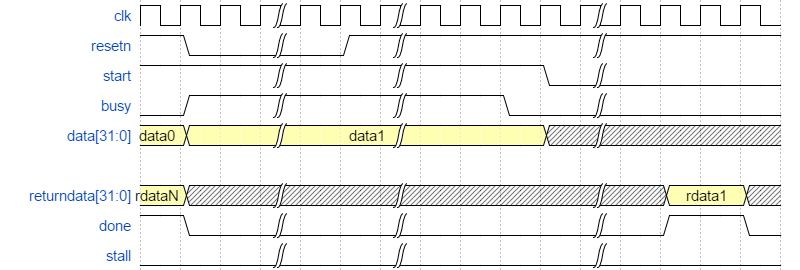

When the reset is asserted, the component holds its busy signal high and its done signal low. After the reset is deasserted, the component holds its busy signal high until the component is ready to accept the next invocation. All component interfaces (agents, hosts, and streams) are ready only after the component busy signal is low.

Simulation Component Reset

You can check the reset behavior of your component during simulation by using the ihc_hls_sim_reset API. This API returns 1 if the reset was exercised (that is, if the reset is called during hardware simulation of the component). Otherwise, the API returns 0.

int ihc_hls_sim_reset(void);During x86 emulation of your component, the ihc_hls_sim_reset API always returns 0. You cannot reset a component during x86 emulation.