Visible to Intel only — GUID: ama1656948059706

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure

2.4. Using the Node Finder

2.5. Analysis & Elaboration Flow

2.6. Design Synthesis

2.7. Design Place and Route

2.8. Incremental Optimization Flow

2.9. Fast Forward Compilation Flow

2.10. Full Compilation Flow

2.11. Compilation Monitoring Mode

2.12. Exporting Compilation Results

2.13. Integrating Other EDA Tools

2.14. Compiler Optimization Techniques

2.15. Synthesis Language Support

2.16. Synthesis Settings Reference

2.17. Fitter Settings Reference

2.18. Design Compilation Revision History

2.6.3.1. Registering the SDC-on-RTL SDC File

2.6.3.2. Applying the SDC-on-RTL Constraints

2.6.3.3. Inspecting SDC-on-RTL Constraints

2.6.3.4. Creating Constraints in SDC-on-RTL SDC Files

2.6.3.5. Using Entity-Based SDC-on-RTL Constraints

2.6.3.6. Types of SDC Files Used in the Intel® Quartus® Prime Software

2.6.3.7. Example: Using SDC-on-RTL Features

2.12.1. Exporting a Version-Compatible Compilation Database

2.12.2. Importing a Version-Compatible Compilation Database

2.12.3. Creating a Design Partition

2.12.4. Exporting a Design Partition

2.12.5. Reusing a Design Partition

2.12.6. Viewing Quartus Database File Information

2.12.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: ama1656948059706

Ixiasoft

2.6.3.1. Registering the SDC-on-RTL SDC File

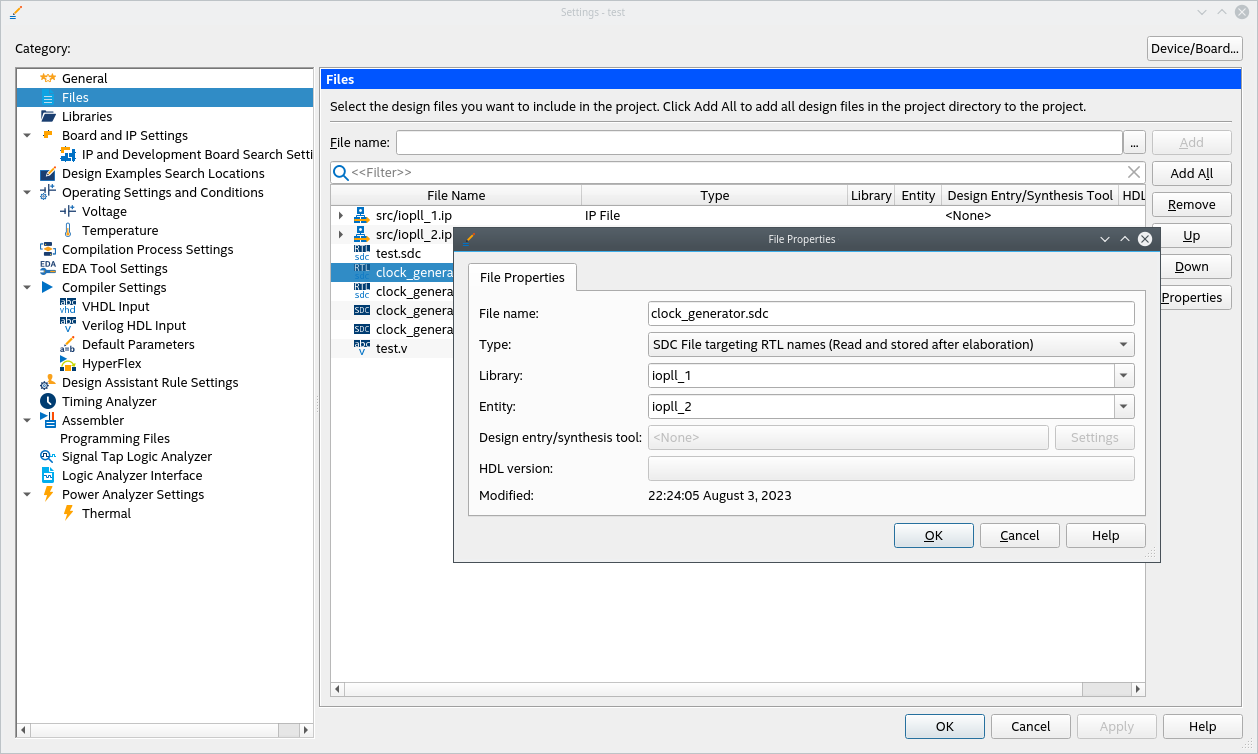

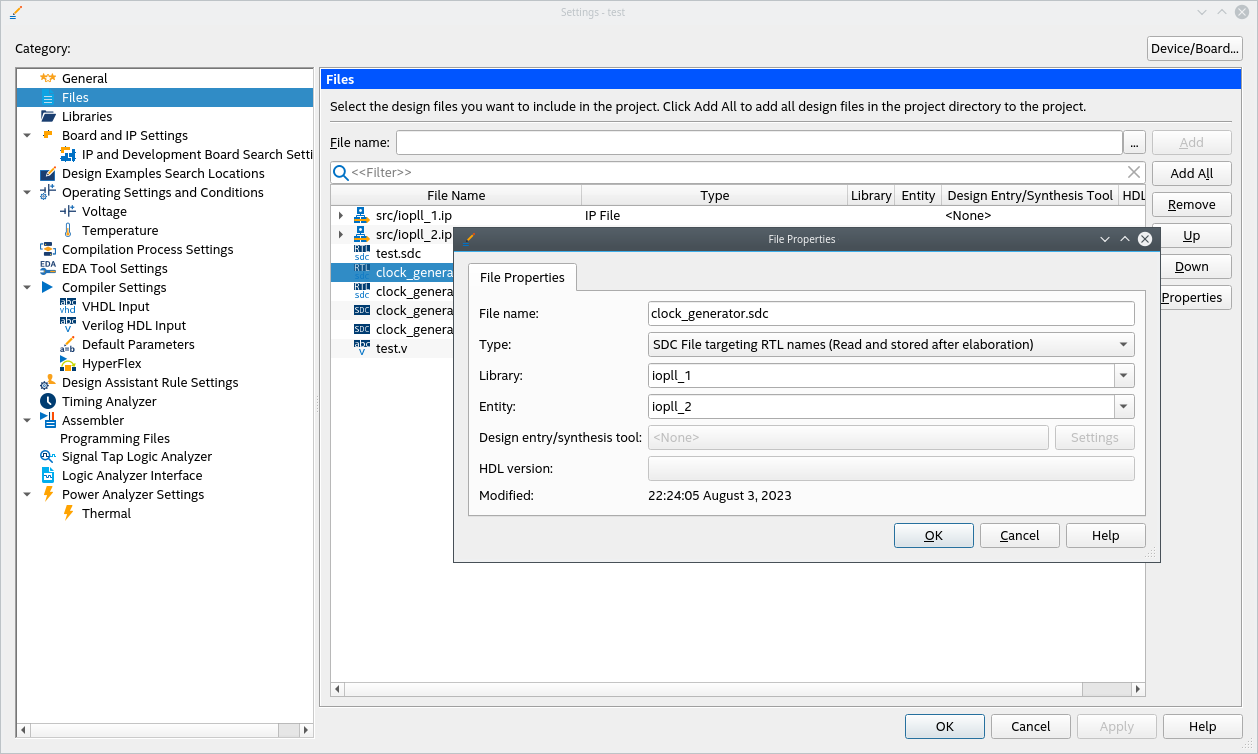

For the Post-Synthesis Static Timing Analysis (STA), your design must include an associated SDC-on-RTL SDC file. You can use the GUI to register an SDC-on-RTL file with your current project from the File Properties dialog by specifying its type as SDC File Targeting RTL names, as shown in the following image:

Figure 41. Registering the SDC-on-RTL SDC File

Note: Alternatively, you can also associate an SDC-on-RTL file with your project from the Timing Analyzer's Constraints > Read SDC File option.

SDC-on-RTL files are registered with an Intel® Quartus® Prime software project through the following RTL_SDC_FILE assignment:

set_global_assignment -name RTL_SDC_FILE sdc_on_rtl_file.sdc

Note: Although you can use any file extension, Intel® recommends using an intuitive file extension, for example, rtlsdc, to help distinguish SDC-on-RTL SDC files from the conventional Intel® Quartus® Prime software SDC files if your design uses both.