Intel® Quartus® Prime Standard Edition User Guide: Design Optimization

Visible to Intel only — GUID: mwh1409960096878

Ixiasoft

Visible to Intel only — GUID: mwh1409960096878

Ixiasoft

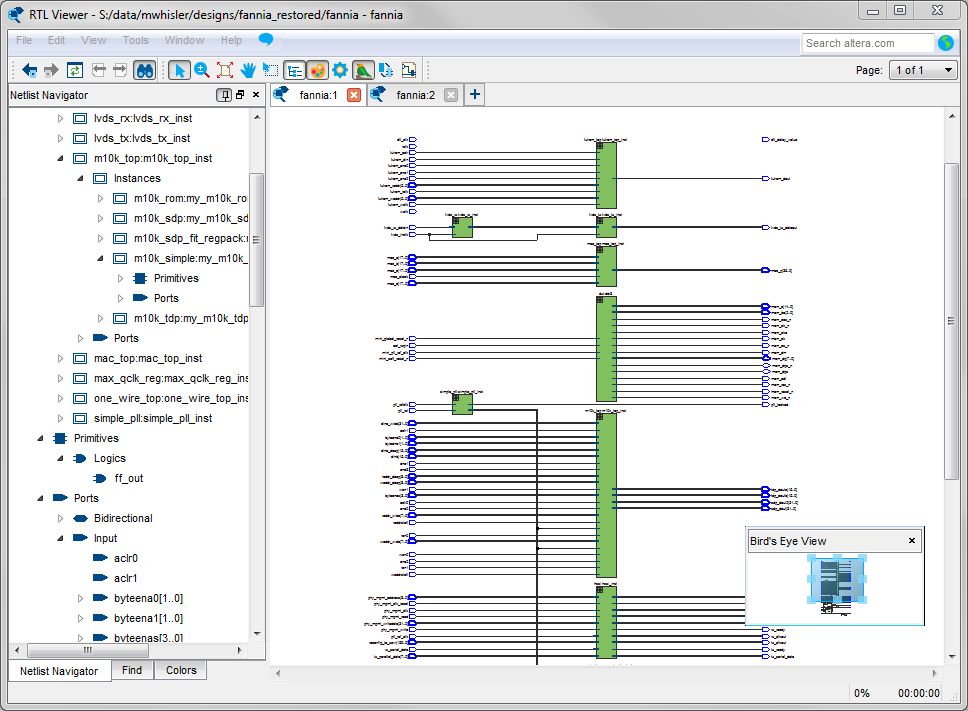

2.6. Netlist Viewer User Interface

The RTL Viewer and Technology Map Viewer each consist of these main parts:

- The Netlist Navigator pane—displays a representation of the project hierarchy.

- The Find pane—allows you to find and locate specific design elements in the schematic view.

- The Properties pane displays the properties of the selected block when you select Properties from the shortcut menu.

- The schematic view—displays a graphical representation of the internal structure of the design.

Netlist Viewers also contain a toolbar that provides tools to use in the schematic view.

- Use the Back and Forward buttons to switch between schematic views. You can go forward only if you have not made any changes to the view since going back. These commands do not undo an action, such as selecting a node. The Netlist Viewer caches up to ten actions including filtering, hierarchy navigation, netlist navigation, and zoom actions.

- The Refresh button to restore the schematic view and optimizes the layout. Refresh does not reload the database if you change the design and recompile.

- Click the Find button opens and closes the Find pane.

- Click the Selection Tool and Zoom Tool buttons to alternate between the selection mode and zoom mode.

- Click the Fit in Page button resets the schematic view to encompass the entire design.

- Use the Hand Tool to change the focus of the viewer without changing the perspective.

- Click the Area Selection Tool to drag a selection box around ports, pins, and nodes in an area.

- Click the Netlist Navigator button to open or close the Netlist Navigator pane.

- Click the Color Settings button to open the Colors pane where you can customize the Netlist Viewer color scheme.

- Click the Display Settings button to open the Display pane where you can specify the following settings:

- Show full name or Show only <n> characters. You can specify this separately for Node name, Port name, Pin name, or Bus name.

- Turn Show timing info on or off.

- Turn Show node type on or off.

- Turn Show constant value on or off.

- Turn Show flat nets on or off.

Figure 4. Display Settings

- The Bird's Eye View button opens the Bird's Eye View window which displays a miniature version of the design and allows you to navigate within the design and adjust the magnification in the schematic view quickly.

- The Show/Hide Instance Pins button can alternate the display of instance pins not displayed by functions such as cross-probing between a Netlist Viewer and Timing Analyzer. You can also use this button to hide unconnected instance pins when filtering a node results in large numbers of unconnected or unused pins. The Netlist Viewer hides Instance pins by default.

- If the Netlist Viewer display encompasses several pages, the Show Netlist on One Page button resizes the netlist view to a single page. This action can make netlist tracing easier.

You can have only one RTL Viewer, one Technology Map Viewer (Post-Fitting), one Technology Map Viewer (Post-Mapping), and one State Machine Viewer window open at the same time, although each window can show multiple pages, each with multiple tabs. For example, you cannot have two RTL Viewer windows open at the same time.