Visible to Intel only — GUID: zxz1547062637786

Ixiasoft

Visible to Intel only — GUID: zxz1547062637786

Ixiasoft

3.1.2. Intel® Agilex™ 7 F-Series and I-Series EMIF Architecture: I/O SSM

The I/O SSM includes dedicated memory which stores both the calibration algorithm and calibration run-time data. The hardened Nios® II processor and the dedicated memory can be used only by an external memory interface, and cannot be employed for any other use. The I/O SSM can interface with soft logic, such as the debug toolkit, via an Avalon® memory-mapped interface bus.

The I/O SSM is clocked by the on-chip configuration network, and therefore does not consume a PLL.

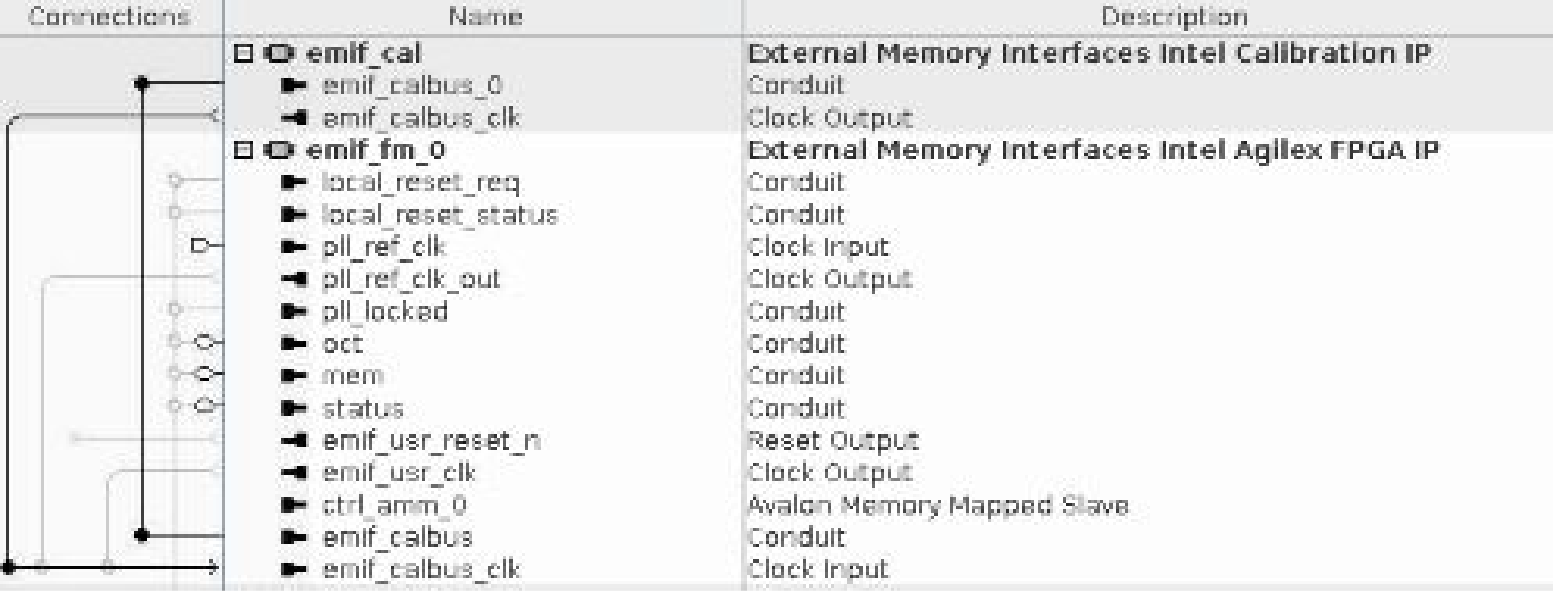

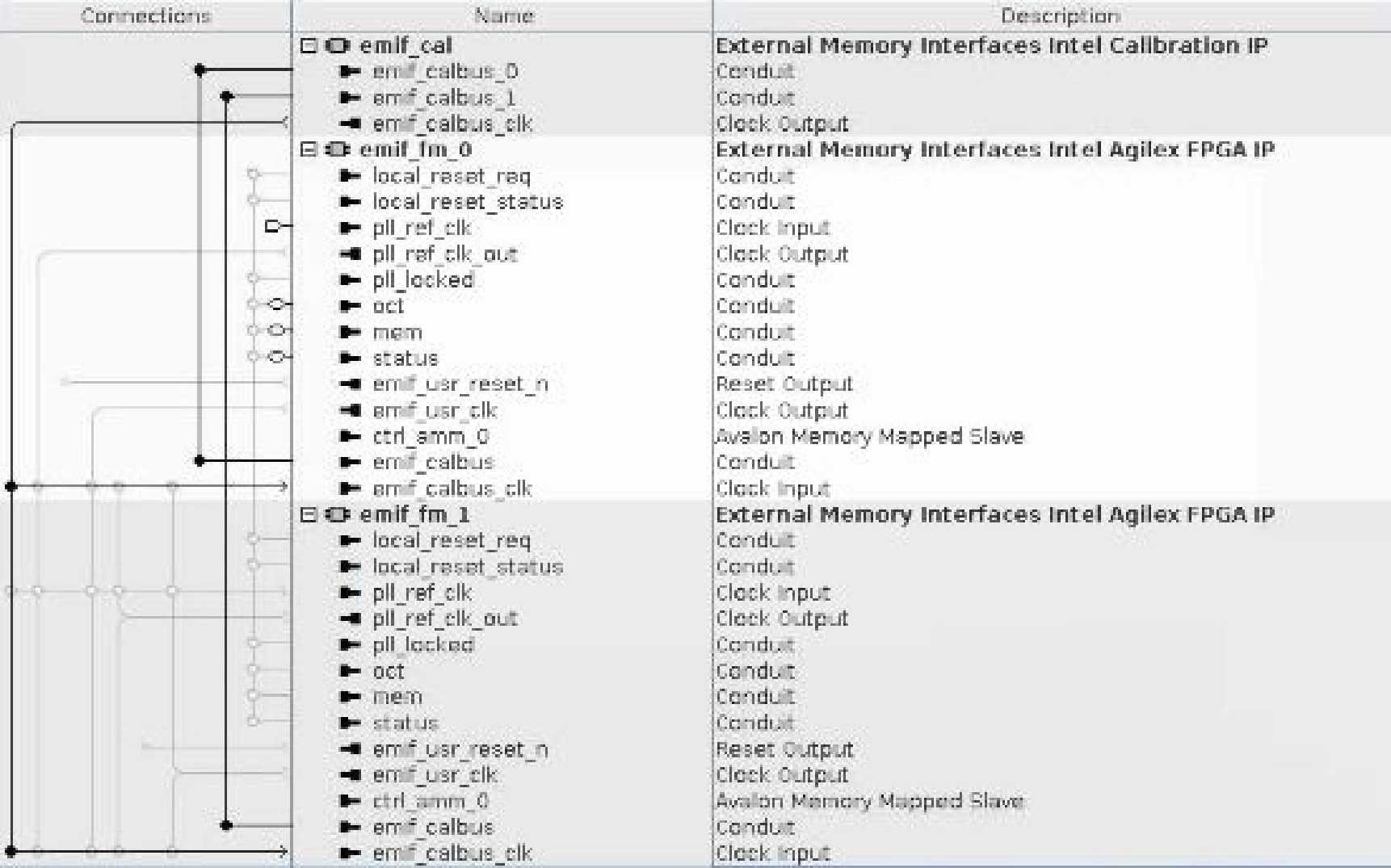

Each EMIF instance must be connected to the I/O SSM through the External Memory Interfaces Calibration IP. The Calibration IP exposes a calibration bus master port, which must be connected to the slave calibration bus port on every EMIF instance.

Only one calibration IP is allowed for each I/O row. All the EMIFs in the same I/O row must be connected to the same calibration I/P. You can specify the number of EMIF interfaces to be connected to the calibration IP when parameterizing the IP. Connect the emif_calbus and emif_calbus_clk on the calibration IP to the emif_calbus and emif_calbus_clk, respectively, on the EMIF IP core.