Visible to Intel only — GUID: mjh1591107604400

Ixiasoft

Visible to Intel only — GUID: mjh1591107604400

Ixiasoft

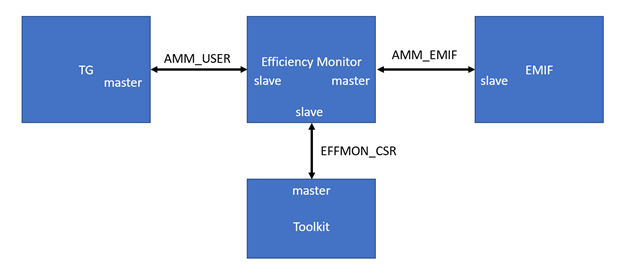

11.11.2. Efficiency Monitor Block Descriptions

amm_emif interface

The Efficiency Monitor passes traffic downstream to the external memory interface on this interface.

amm_user interface

The traffic generator (or custom user logic) initiates traffic and passes it to the Efficiency Monitor over this interface.

effmon_csr interface

This interface consists of several configuration and status registers. The Efficiency Monitor Mode parameter controls whether this interface is exported for you to provide a custom master, or connected internally so that the System Console can act as master on this interface.