Visible to Intel only — GUID: jks1622038206603

Ixiasoft

1. About the External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP

3. Design Example Description for External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP

4. External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP Design Example User Guide Archives

5. Document Revision History for External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Generating the Synthesizable EMIF Design Example

2.4. Generating the EMIF Design Example for Simulation

2.5. Simulation Versus Hardware Implementation

2.6. Simulating External Memory Interface IP With ModelSim

2.7. Pin Placement for Intel® Agilex™ 7 F-Series and I-Series EMIF IP

2.8. Compiling and Programming the Intel® Agilex™ 7 F-Series and I-Series EMIF Design Example

2.9. Generating a Design Example with the Calibration Debug Option

2.10. Generating a Design Example with the TG Configuration Option

2.11. Using the Design Example with the EMIF Debug Toolkit

Visible to Intel only — GUID: jks1622038206603

Ixiasoft

2.10.1. Enabling the Traffic Generator in a Design Example

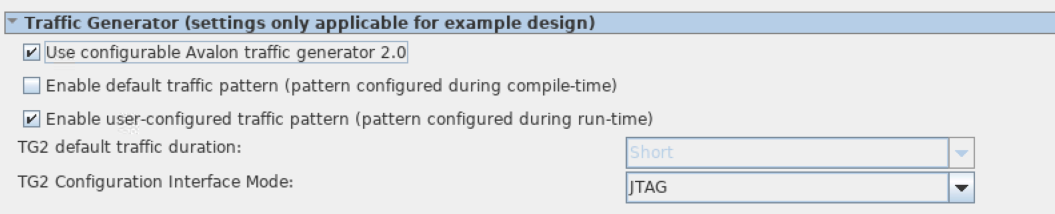

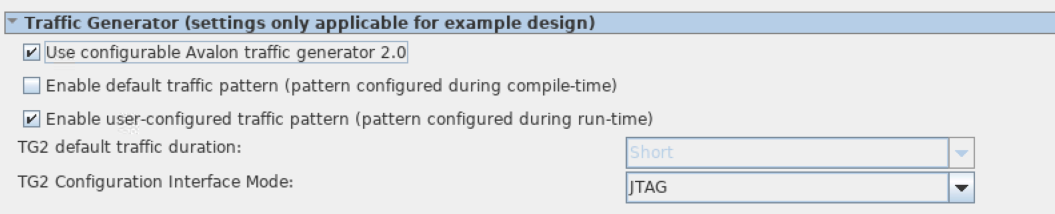

You can enable the configurable traffic generator from the Diagnostics tab in the EMIF parameter editor.

To enable the configurable traffic generator, turn on Use configurable Avalon traffic generator 2.0 on the Diagnostics tab.

Figure 6.

- You may choose to disable the default traffic pattern stage or the user-configured traffic stage, but you must have at least one stage enabled. For information on these stages, refer to Default Traffic Pattern and User-configured Traffic Pattern in the External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP User Guide.

- The TG2 test duration parameter applies only to the default traffic pattern. You may choose a test duration of short, medium, or infinite.

- You may choose either of two values for the TG2 Configuration Interface Mode parameter:

- JTAG: Allows use of a GUI in the system console. For more information, refer to Traffic Generator Configuration User Interface in the External Memory Interfaces Intel® Agilex™ 7 F-Series and I-Series FPGA IP User Guide.

- Export: Allows use of custom RTL logic to control the traffic pattern.