Visible to Intel only — GUID: ixz1575513745817

Ixiasoft

Visible to Intel only — GUID: ixz1575513745817

Ixiasoft

50.4.3. Receive Interface

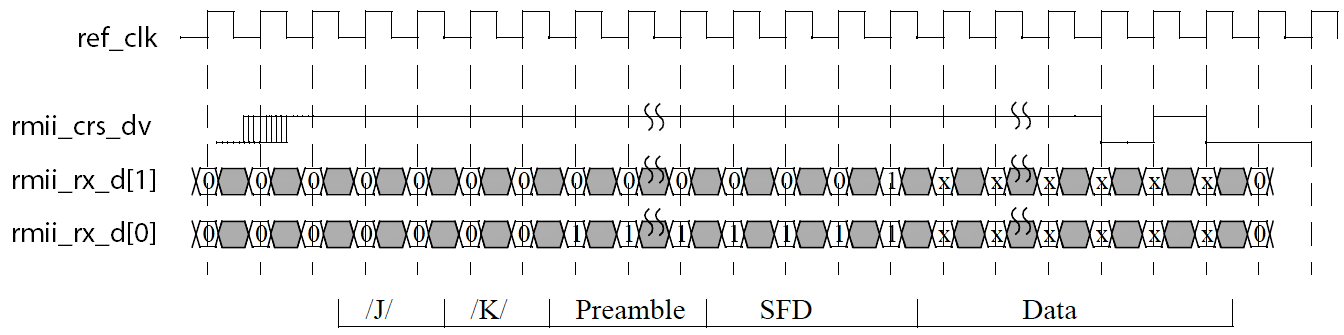

The PHY asserts the Carrier Sense or Receive Data Valid (rmii_crs_dv) signal when the receive medium is non-idle. The rmii_crs_dv is de-asserted synchronously if the carrier is lost, but only at nibble boundaries. If the PHY has additional bits to be presented on rmii_rx_d[1:0] following the loss of carrier, the PHY asserts the rmii_crs_dv on cycles of ref_clk which represent the second di-bit of each nibble.

At the nibble boundary, the rmii_crs_dv toggles at 25 MHz in 100 Mbps mode and 2.5 MHz in 10 Mbps mode on the event of carrier loss. This helps the IP core to recover the receive data valid and carrier sense signal.